## Portland State University

# PDXScholar

Computer Science Faculty Publications and Presentations

**Computer Science**

1-1992

# Porting the Chorus Supervisor and Related Low-Level Functions to the PA-RISC

Ravi Konuru Oregon Graduate Institute of Science & Technology

Marion Hakanson Oregon Graduate Institute of Science & Technology

Jon Inouye Oregon Graduate Institute of Science & Technology

Jonathan Walpole Oregon Graduate Institute of Science & Technology

Follow this and additional works at: https://pdxscholar.library.pdx.edu/compsci\_fac

Part of the Computer and Systems Architecture Commons, and the Computer Sciences Commons Let us know how access to this document benefits you.

# **Citation Details**

"Porting the Chorus Supervisor and Related Low-Level Functions to the PA-RISC," Ravi Konuru, Marion Hakanson, Jon Inouye and Jonathan Walpole, OGI Technical Report No. CS/E-92-006, January 1992.

This Technical Report is brought to you for free and open access. It has been accepted for inclusion in Computer Science Faculty Publications and Presentations by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

# Porting the Chorus *Supervisor* and Related Low-level Functions to the PA-RISC

Ravindranath Konuru, Marion Hakanson, Jon Inouye, Jonathan Walpole;

Department of Computer Science and Engineering Oregon Graduate Institute of Science and Technology

January 27, 1992

### Abstract

This document is part of a series of reports describing the design decisions made in porting the Chorus Operating System to the Hewlett-Packard 9000 Series 800 workstation.

The Supervisor is the name given by Chorus to a collection of low-level functions that are machine dependent and have to be implemented when Chorus is ported from one machine to another. The Supervisor is responsible for interrupt, trap and exception handling, managing low-level thread initialization, context switch, kernel initialization, managing simple devices (timer and console) and offering a low-level debugger [7]. This document describes the port of the Supervisor and related low-level functions.

The information contained in this paper will be of interest to people who wish to understand:

- The main characteristics of Chorus and PA-RISC architecture that are useful in understanding the port of the Chorus *Supervisor*.

- The requirements and implementation of the Chorus Supervisor .

- The requirements and implementation of Chorus page fault interface

- The requirements and implementation Chorus System Call Interface

- The requirements and implementation of *mutex* interface which is a part of the Chorus system call interface for efficient thread synchronization.

- Reasons for the modifications to the portable layers of Chorus kernel to implement the above requirements. A summary of the modifications is also presented.

It is useful to read the port overview [17] before reading this document. It is also a good idea to have the *Precision Architecture and Instruction Set Reference Manual* [10] and Chorus v3.3 implementation guide[7] on hand although it is not absolutely necessary.

<sup>\*</sup>This research is supported by the Hewlett-Packard Company (HP), Chorus Systémes, and Oregon Advanced Computing Institute (OACIS).

# Contents

| 1 | Intr | oduction                                               | 4        |

|---|------|--------------------------------------------------------|----------|

|   | 1.1  | Supervisor Port Overview                               | 4        |

|   | 1.2  | Chorus Overview                                        | <b>5</b> |

|   | 1.3  | PA-RISC                                                | 5        |

|   |      |                                                        | 7        |

|   |      |                                                        | 8        |

|   |      |                                                        | 9        |

|   |      |                                                        |          |

| 2 | Sup  | ervisor 1                                              | 2        |

|   | 2.1  | Supervisor requirements                                | 13       |

|   |      | 2.1.1 Supervisor interface requirements                | 13       |

|   |      | 2.1.2 Supervisor Actor Interface                       | 17       |

|   |      | 2.1.3 Event (Interrupt, Trap and Exception) Handling 1 | 8        |

|   |      |                                                        | 8        |

|   |      |                                                        | 8        |

|   |      |                                                        | 9        |

|   | 2.2  |                                                        | 9        |

|   |      |                                                        | 9        |

|   |      |                                                        | 21       |

|   |      |                                                        | 21       |

|   |      |                                                        | 24       |

|   |      |                                                        | 25       |

|   |      |                                                        | 25       |

|   |      |                                                        | 25       |

|   |      |                                                        | 26       |

|   |      |                                                        | 29       |

|   |      |                                                        | 32       |

|   |      |                                                        | 32       |

|   |      |                                                        | 94<br>37 |

|   |      |                                                        |          |

|   |      | <b>0</b>                                               | 37       |

|   |      | 2.2.14 Kernel Initialization 3                         | 88       |

| 3 | Che  | rus Page Fault Interface 3                             | 9        |

|   |      |                                                        | 39       |

|   | 3.2  |                                                        | 39       |

|   | 0.2  |                                                        | ).)      |

| 4 | Svs  | em Call Interface 4                                    | 1        |

|   | 4.1  |                                                        | 11       |

|   | 4.2  |                                                        | 12       |

|   |      | 1                                                      | 12       |

|   |      |                                                        | 45       |

|   |      |                                                        | U        |

| 5 | Mu   | ex Interface 4                                         | 6        |

|   | 5.1  | Requirements                                           | 16       |

|   | 5.2  | Implementation                                         | 17       |

| 6 | Modifications to the Chorus Portable Layers | 49 |

|---|---------------------------------------------|----|

| 7 | Future Work                                 | 50 |

| 8 | Acknowledgements                            | 51 |

# 1 Introduction

This document is part of a series of reports describing the design decisions made in porting the Chorus Operating System to the Hewlett-Packard 9000 Series 800 workstation.

Chorus is horizontally divided into a machine independent layer and a machine dependent layer. The machine dependent layer exports a machine *independent* interface that is expected to remain unchanged as the operating system is ported from one machine to another. The machine dependent layer is divided vertically into two major partitions: the *Supervisor* and the *mmu* (memory management unit). The *mmu* is responsible for the implementing the machine dependent memory management functions [1]. This document deals with the implementation of the *Supervisor* and other related low-level functions. The port of the *mmu* is discussed elsewhere [11].

An overview of the port of the Chorus Supervisor and related functions is given in section 1.1. Brief reviews of some of the characteristics of Chorus and the PA-RISC architecture are given in sections 1.2 and 1.3 respectively. The purpose of these reviews is to give sufficient background for discussing the machine dependent layer. For detailed information about Chorus, refer to the Chorus technical reports CS/TR-90-71 [7] and CS/TR-89-36.1 [2]. For information about PA-RISC, refer to [15, 10].

The Supervisor requirements and implementation are presented in section 2. The Chorus page fault interface is presented in section 3, the System call interface in section 4, and the mutex interface in section 5.

The main reasons for the modifications to the portable layers of the Chorus kernel and a summary of the modifications is given in section 6. Future work is presented in section 7.

### 1.1 Supervisor Port Overview

We started our ground work for the port in Sep 90. The operating system as well as the architecture were completely new to us at that time. We spent about a month reading the documentation and papers on PA-RISC architecture [10, 15, 16, 13] and Chorus operating system [2, 1, 4]. The **Tut** books [8, 3] documenting the mach 2.0 port by HP to PA-RISC proved valuable sources of information.

In Oct 90 we had a 1-week course on porting Chorus at Chorus Systémes, France. Various components were identified. As Chorus personnel were also not familiar with PA-RISC, the Chorus port to Motorola 88000 was used as a case study to explain the various machine dependent components and the porting process. This proved useful for the design of the Chorus Supervisor.

Assembly language programs were written to understand the PA-RISC architecture especially with respect to nullification, delayed branches, procedure calling conventions and the usage of adb, the assembly language debugger.

The following basic principles of design were applied as often as possible:

- Use 32 bit addresses. Initially, we considered using 64-bit addresses. However, it would have caused extensive changes in the portable layers of the kernel and is was not clear how to design an interface with 64-bit address parameters. In any case, it would have increased the time of the port. We left this for future work.

- Keep the design as simple as possible. The aim was to get the first working port as quickly as possible. This was one of the principles that was reiterated during our course at France. We whole heartedly agreed with that.

• Use the available **Tut** code for the machine dependent layer implementation. The goal again was to get the port up as quickly as possible. For example the code for initialization would have taken us a long time to figure out, write and debug if did not use the **Tut** code albeit with modifications.

The design and implementation of the *Supervisor* did not prove very difficult once we had a good grasp of the architecture and the Chorus machine dependent layer. The availability of **Tut** code was also very beneficial.

Chorus provides a kernel test suite[9] for validating the kernel. This was the only method we employed to validate our kernel port.

# 1.2 Chorus Overview

Chorus is a message based micro-kernel that supports the following abstractions<sup>1</sup>:

- Actor

- Thread

- Message

- Port

An Actor forms the unit of resource allocation and identifies a protected address space. An address space is split into a **user address space** and **system address space**. On a given site<sup>2</sup>, each actor's system address space is identical and its access is restricted to privileged levels of execution. An actor in Chorus can be a Supervisor actor or User Actor. A supervisor actor lives in the system address space along with the kernel. Supervisor actors have higher privilege than user Actors.

A thread is the basic unit of execution and runs in the context of an Actor. A thread is a sequential flow of control and is characterized by a thread context corresponding to the state of the processor at any given point during the execution of thread. There can be multiple threads per actor.

Threads communicate and synchronize by exchanging messages between their actors' ports. Threads sharing the same address space can use share memory for communication and synchronization. Semaphores and Mutexes provided by the Chorus interface are useful for this purpose.

A thread belonging to a user Actor is called a user thread. However during a system call, it becomes a supervisor thread. A user thread has 2 stacks: a user stack for executing user code and a system stack for executing system calls, traps, and storing the context of the thread when the thread is blocked. A thread belonging to a supervisor actor is called a supervisor thread. Since a supervisor thread lives entirely in the system address space, it has only a system stack and no user stack.

# 1.3 PA-RISC

This section consists of extracts from the PA-RISC architecture reference manual useful for understanding the machine dependent layer implementation. For more details see the cited references.

<sup>&</sup>lt;sup>1</sup>Chorus is written in an object oriented language C++. These abstractions are implemented as C++ classes

$<sup>^{2}</sup>$ A site is a grouping of tightly-coupled resources controlled by a single Chorus Nucleus[6]

PA-RISC Architecture is the frame work for Hewlett-Packard's HP3000/900, HP9000/800, and HP9000/700 series computer systems.

It is based on the principles of RISC and has 140 fixed length instructions. It employs a virtually addressed cache and the I/O sub-system is memory mapped. PA-RISC supports 48-bit, 56-bit or 64-bit virtual addresses and provides some hardware protection support. The global virtual memory is organised as a set of linear spaces with each space being 4 gigabytes  $(2^{32})$  long. Each space is specified with a space identifier.

PA-RISC supports 4 privilage levels numbered 0-3. The highest privilege level is 0 and the lowest privilege level is 3.

PA-RISC architecture has the following resources:

- 32 General Registers. GR0 is tied permanently to zero. GR1 is the target of Addil instructions. GR31 is the link register for an inter-space branch and link external (Ble) instruction. GR27 used as the base pointer for data accesses. This is specified by the procedure calling conventions of the architecture.

- 25 Control Registers. CR1-CR7 do not exist. Control registers are discussed in more detail in the section 1.3.1.

- 8 Space Registers. SR0 is the instruction address space link Register for Ble instruction. SR0-SR4 can be modified at any privilege level. SR5-SR7 can be modified at privilege level 0. The usage of the space registers is left to the operating system. The space registers are 16-bit long on a level 1 PA-RISC, 24-bit long on a level 1.5 PA-RISC and 32-bit long on a level 2 PA-RISC. On a level 0 PA-RISC, the space registers do not exist. A level 0 PA-RISC supports absolute addressing only.

- Processor Status Word (PSW) The processor state is encoded in a 32-bit register PSW. PSW does not appear as an operand in instructions. When an *interruption* <sup>3</sup> occurs, the old value of the PSW is saved in the IPSW register(CR22). Some of the bits in the PSW are reserved. It is software's responsibility that these are zero when written. The PSW is set from IPSW by a *return from* interruption instruction.

The PSW bits that are important for the discussion are:

- C bit (PSW<sub>-</sub>C) Code (instruction) address translation enable. When 1, instruction addresses are translated and access rights checked.

- Q bit (PSW\_Q) Interruption Collection Enable. When 1, *interruption* state is collected. When an *interruption* occurs the details of the instruction being executed are recorded in the control registers (see 1.3.1).

- P bit (PSW\_P) Protection Identifier enable. When this bit and the C-bit are both 1, instruction references check for valid protection identifiers(PIDs). When this bit and the D-bit are both 1, data references check for valid PIDs. When this bit is 1, probe instructions check for valid PIDs.

- D bit (PSW\_D) Data address translation enable. When 1, data addresses are translated and access rights checked.

- I bit (PSW\_I) External interrupt, power failure interrupt, and low-priority machine check interrupt unmask. When 1, these interrupts are unmasked and can cause an interrupt. when 0 the interrupts are held pending.

<sup>&</sup>lt;sup>3</sup>An interruption is PA-RISC specific term. An interruption is a trap or an interrupt that can occur on PA-RISC.

• Instruction Address queues.

The instruction Address queues hold the address of the currently executing instruction and the address of the instruction that will be executed after the current instruction, termed the *following* instruction. There are 2 queues: Instruction Address Space Queue (IASQ) and the Instruction Address Offset Queue(IAOQ). Each queue is 2 elements deep. The elements are referred to IAOQ\_FRONT, IAOQ\_BACK, IASQ\_FRONT and IASQ\_BACK. The 2-deep queues are used to support the delayed branching capability.

# 1.3.1 Control Registers

This section defines the main registers used in the implementation:

- Protection Identifier Registers: PID1, PID2, PID3, PID4, aliases for CRs 8, 9, 12, and 13. These registers designate up to four groups of pages accessible to the currently executing process. When translation is enabled, the four protection identifiers (PIDs) are compared with a page access identifier to validate access. If access is not valid trap is raised.

- Coprocessor Configuration Register (CR10 alias CCR) is an 8-bit register which records the presence and usability of coprocessors. A bit is 1 implies the coprocessor corresponding to that bit is present and operational. Else it is logically decoupled. In the current implementation the entire CCR is set to 0.

- *interruption* Vector Address Register (CR14 alias IVA) contains the **absolute address** of the base of an array of service procedures assigned to the interruption classes. This address must be a multiple of 1024.

- External Interrupt Enable Mask (CR15 alias EIEM) is a 32-bit register containing a bit for each of the 32 external interrupts. When 0, bits in the EIEM mask interrupts pending for the external interrupts corresponding to those bit positions.

- External Interrupt Request Register (CR23 alias EIRR) is a 32-bit register containing a bit for each external interrupt. When 1, a bit designates that an interrupt is pending for the corresponding external interrupt. Both the PSW\_I bit and the corresponding bit position in the EIEM must be 1 for an interrupt to occur.

- Interval Timer Register (CR16 alias ITMR) consists of 2 internal registers. One of the internal registers is continually counting up by 1. Reading the ITMR gives the value of this internal register. Writing to ITMR updates the other (comparison) register. When the two registers have identical values, an external interrupt is raised and bit 0 of EIRR is set to 1.

- *interruption* Instruction Address Space and Offset Queues (CR17 alias IIASQ, CR18 alias IIAOQ): Two offset registers and two space registers are used to save the instruction address and and privilege level information for use in processing interruptions. The registers are arranged as two two-element deep queues. The queues generally contain the address(including the privilege level field in the rightmost two bits of the offset part) of the two instructions in the IA queues at the time of the interruption.

The IIA queues are continually updated whenever the PSW\_Q bit is 1 and are frozen by an interruption (PSW\_Q) bit becomes 0. After such an interruption these registers contain copies of the IA queues. These queue elements will also be referred to as PCOQII, PCOQT, PCSQII and PCSQT in the context of the implementation. • Interruption parameter registers are the Interruption Instruction Register (CR19 alias IIR), Interruption Space Register (CR20 alias ISR) and Interruption Offset Register (CR21 alias IOR). As the names indicate, these registers contain interrupted instruction and the virtual address the instruction was attempting to access.

### 1.3.2 Interruptions

| Interruption # | Description                                               |  |  |  |

|----------------|-----------------------------------------------------------|--|--|--|

| 1              | High-priority machine check                               |  |  |  |

| 2              | Power failure interrupt                                   |  |  |  |

| 3              | Recovery counter trap                                     |  |  |  |

| 4              | External interrupt                                        |  |  |  |

| 5              | Low-priority machine check                                |  |  |  |

| 6              | Instruction TLB miss fault                                |  |  |  |

| 7              | Instruction memory protection trap                        |  |  |  |

| 8              | Illegal instruction trap                                  |  |  |  |

| 9              | Break instruction trap                                    |  |  |  |

| 10             | Privileged operation trap                                 |  |  |  |

| 11             | Privileged register trap                                  |  |  |  |

| 12             | Overflow trap                                             |  |  |  |

| 13             | Conditional trap                                          |  |  |  |

| 14             | Assist exception trap                                     |  |  |  |

| 15             | Data TLB miss fault                                       |  |  |  |

| 16             | Non-access instruction TLB miss fault                     |  |  |  |

| 17             | Non-access data TLB miss fault                            |  |  |  |

| 18             | Data memory protection trap/Unaligned data reference trap |  |  |  |

| 19             | Data memory break trap                                    |  |  |  |

| 20             | TLB dirty bit trap                                        |  |  |  |

| 21             | Page reference trap                                       |  |  |  |

| 22             | Assist emulation trap                                     |  |  |  |

| 23             | Higher-privilege transfer trap                            |  |  |  |

| 24             | Lower-privilege transfer trap                             |  |  |  |

| 25             | Taken Branch trap                                         |  |  |  |

Table 1: PA-RISC Interruption

All *interruptions* (traps or interrupts) on PA-RISC are precise, i.e., the software sees a single unpipelined processor executing one instruction at a time. PA-RISC supports 25 interruptions divided into 4 priority groups, with group 1 having the highest priority and group 4 the lowest. The interruptions are listed in table 1.

Interruption 1 belongs to group 1. Interruptions 2-5 belong to group 2. Interruptions 6-22 belong to group 3 and the rest to group 4.

#### **1.3.3** Memory Management Support

Like most microprocessor architectures, the PA-RISC contains some form of memory management unit (MMU).

This section describes the features of the PA-RISC that are used to support virtual memory operations. These features include a translation look-aside buffer (TLB) for transforming virtual addresses to physical addresses, bit traps for memory management support, and memory protection mechanisms. The material presented in this section is covered in more detail in chapter 3 of the *Precision Architecture and Instruction Set Reference Manual* [10].

### Page Tables and the TLB :

The PA-RISC (along with the MIPS R2000/R3000) is unusual in that it requires software to handle TLB misses<sup>4</sup>. By allowing software to perform TLB loads, the PA-RISC architecture gives the operating system lots of flexibility in the format of page tables. Normally, architectures specify some page table format to follow so the hardware can perform TLB loads.

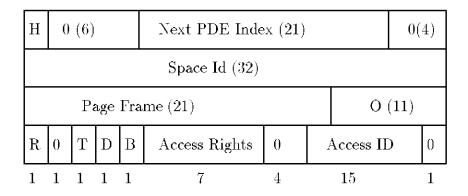

Rather than develop our own page table design for the initial port, we decide to use the *Physical Page Directory (PDIR)* format suggested by the PA-RISC architecture manual [10]. We made this decision because it allowed us to reuse a great deal of **Tut** code for the low level TLB miss handlers. Figure 1 shows the structure of a Physical Page Directory (PDIR) entry.

Figure 1: PDIR Entry (PDE)

### Bit Flags :

The TLB and PDIR contain a variety of bit flags which can be used to generate traps. The following information describes the function of each of the 1-bit fields.

- T Page Reference Trap. When 1, data references using this translation cause a page reference trap interruption. The T-bit is most commonly used for program debugging.

- D Dirty. When 0, store and semaphore instructions cause a TLB dirty bit trap on systems with software TLB miss handling. When 0, store and semaphore instructions cause the D-bit in

<sup>&</sup>lt;sup>4</sup>The *PA-RISC Architecture and Instruction Set Manual* mentions that hardware implementations can exist but to our knowledge no such implementation exists at this time.

the DTLB entry and the PDIR to be set to 1 on systems with hardware TLB miss handling. When 1, no trap or update occurs. The D-bit may be used by the operating system to determine which pages have been modified.

- B Break. When 1, instructions that could modify data using this translation cause a data memory break trap interruption, if enabled. Store instructions, the PURGE DATA CACHE instruction, and semaphore instructions are the only instructions that potentially modify data. The B-bit is most commonly used for program debugging.

- R is the reference bit (only present in the PDIR entry). If R = 1, the page has been accessed (read, write, execute, or non-access) by a processor since the bit was last set to 0. For systems with software TLB miss handling, this bit is managed by the software and not directly set by the hardware.<sup>5</sup>

### **Memory Protection :**

The TLB is also responsible for enforcing memory protection. The PA-RISC protection mechanisms are disabled when physical addressing is used or when the PSW\_P bit is disabled. The TLB maintains protection information in two fields: the *access rights* and the *access ID*. The 7-bit access right field encodes the allowed access types and privilege levels into three sub-fields: *type*, privilege level 1 (*PL1*), and privilege level 2 (*PL2*). The *access ID* is a 15-bit field that can be thought of as a capability. This field must match one of the four protection ID's in the PA-RISC's control registers (CR8,9,12,13).

### Logical Page Replacement :

The PA-RISC allows the software to operate on a logical page size of 2K, 4K, 8K, or 16K bytes. When operating on a logical page size greater than 2K bytes, the TLB miss handling procedures may insert all translations for that page group provided that the translation for the faulting page is inserted last. This is probably because the software has no ability to know which TLB entry is invalidated to make room for a new insertion. By inserting the faulting page entry last, the software ensures that upon return, the TLB miss has been satisfied.

#### **PA-RISC** Memory Management Traps :

Out of the 25 *interruptions* that can occur on PA-RISC, 9 of the interruptions are traps to be dealt by the memory management unit of the operating system. These memory management traps are listed in table 2.

These traps can be partitioned into four groups: TLB miss faults, non-access TLB miss faults, meory protection faults, and bit flag traps.

### TLB Miss Faults (#6,#15):

The PA-RISC architecture allows both software and hardware TLB miss handling. The IIP 9000/834, the target processor for the port, does not have hardware TLB miss handling. It has separate traps for instruction and data TLB misses with the hardware making no distinction between TLB misses and page faults. When a TLB miss fault occurs, the handler must determine

$<sup>^{5}</sup>$ The unused bit is used by some implementations. This A bit acts similarly to the R bit except non-access faults will not set it.

| Table 2: PA-RISC Memo | ry Management Exceptions |

|-----------------------|--------------------------|

|-----------------------|--------------------------|

| Trap #                                   | Description                                               |  |  |  |

|------------------------------------------|-----------------------------------------------------------|--|--|--|

| 6                                        | Instruction TLB miss fault                                |  |  |  |

| 7                                        | 7 Instruction memory protection trap                      |  |  |  |

| 15                                       | 15 Data TLB miss fault                                    |  |  |  |

| 16 Non-access instruction TLB miss fault |                                                           |  |  |  |

| 17 Non-access data TLB miss fault        |                                                           |  |  |  |

| 18                                       | Data memory protection trap/Unaligned data reference trap |  |  |  |

| 19                                       | Data memory break trap                                    |  |  |  |

| 20                                       | TLB dirty bit trap                                        |  |  |  |

| 21                                       | Page reference trap                                       |  |  |  |

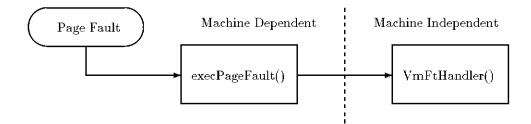

whether or not the missing page is in memory. One disadvantage of an inverted page table(i.e, PDIR) is that it is more expensive to determine whether a particular virtual page is in memory. We use a hashing function and linked list search to determine whether a virtual page entry is present in the PDIR. The handler hashes the faulting (virtual) address to obtain an offset into a hash table. This hash table contains a reference to the PDIR list that represents the hash bin. This bin is organized as a linked list of PDIR entries. The handler then sequentially searches this list for the desired virtual page. A successful match results in the entry being placed in the TLB. A failure in the matching process results in a page fault. Figure 2 presents a flow chart of the steps for handling a TLB miss.

### Non-access TLB miss faults (#16, #17):

The PA-RISC architecture also has the notion of non-access TLB faults which differ from other TLB faults in that the faulting page need not be loaded into memory. Our platform requires both instruction and data non-access TLB miss faults to be handled by software.

Non-access data TLB miss faults are caused by LOAD PHYSICAL ADDRESS (LPA), PROBE, and PURGE/FLUSH DATA CACHE instructions. When the requested page entry is not present in the PDIR, the action of the trap handler depends on the type of instruction causing the fault. For LPA and PROBES, zero is returned if the desired page cannot be found in the PDIR. There is a problem with the PROBE instruction that is covered in more detail in section 3.2.

In HP-UX and **Tut**, cache PURGE and FLUSH instructions that cause non-access TLB miss faults are handled as if a TLB miss occurred, i.e. the page is loaded into physical memory and the page descriptor is inserted into both the PDIR and TLB. Non-access instruction TLB miss faults are caused by FLUSH INSTRUCTION CACHE (FIC) instructions. These are handled similar to other cache non-access faults described above.

### Memory Protection Traps (#7,#18):

The PA-RISC has two traps used to detect memory protection violations. The *instruction* memory protection trap (7) is the result of invalid access rights or invalid protection IDs for an instruction fetch<sup>6</sup>. The *data* memory protection trap (18) is the result of an invalid access right or protection ID for any load, store, semaphore, and PURGE DATA CACHE instruction. This

<sup>&</sup>lt;sup>6</sup>Protection ID checking is only done when the PSW P-bit is set.

Figure 2: TLB Miss Handling

trap is also caused by any load or store to addresses not aligned at the boundaries required by the instructions. Detection of unaligned addresses is performed by examining the least significant bits of the virtual address.

### TLB Dirty, Page reference and Data memory break traps (#20,#21,#19) :

The HP 9000 Series 834 workstation does not have a hardware supported TLB, so the manipulation of the D (dirty) and R (reference) bit flags is left to the operating system.

When the D bit is 0, stores and semaphore operations will cause a *TLB dirty bit trap* (20). The trap handler must then set the D bit in both the PDIR and TLB entry. Once the D bit has been set, further modifications to that page are ignored. If the T bit is set, data reference using the translation causes a *page reference trap* (21). The *data memory break trap* (19) is triggered when instructions that could possibly modify data require the translation and the B bit in the Processor Status Word (PSW) is 1. When software loads an entry into the TLB, it should set the R bit to indicate that the page has been referenced.

# 2 Supervisor

The Supervisor is the component that directly interacts with the underlying hardware. It is responsible for managing interrupts, traps and exceptions and other machine dependent functions. The Supervisor along with the mmu layer forms the machine dependent layer and is expected to offer a machine independent interface to the portable layers of the Chorus kernel. The requirements to be satisfied by the Supervisor layer are detailed in section 2.1 and the implementation is detailed in section 2.2.

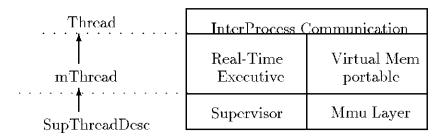

Figure 3: thread Class hierarchy

### 2.1 Supervisor requirements

The Chorus Supervisor is expected to export a specified machine independent interface, and is responsible for interrupt, trap and exception handling, timer and console management, kernel initialization, and offering a low-level debugger. The Supervisor interface is detailed in section 2.1.1. The sections on event handling, timer and console management and low-level debugger regroup the functions in the interface according to their functionality and provide the requirements for the function group as a whole.

In addition to the above functions, the Supervisor is responsible for defining two fundamental structure types : KnThreadCtx, and SupThreadDesc. KnThreadCtx defines the register context frame that is used to save state during interrupts, traps, exceptions and context switches. SupThreadDesc defines the machine dependent thread descriptor. As mentioned in section 1.2, a thread in Chorus has a user stack and a system stack. The descriptor SupThreadDesc keeps track of the stacks and other machine dependent thread attributes (if any) of the thread and is the base class for the Thread class. The Thread class hierarchy is shown in fig 3. The dotted lines show the levels of definition and management of base and derived classes. Variables and pointers of type KnThreadCtx and SupThreadDesc get defined and passed in the portable layers of the kernel but are treated as black boxes. Functions are defined in the Supervisor interface (see section 2.1.1) that allow the portable layers to query and update the contents of the data structures in a machine independent manner.

A portion of the Chorus Interface to supervisor actors allows handlers to be attached for interrupts, traps, exceptions and time-outs. Invocation of some of these handlers is the responsibility of the *Supervisor*. This requirement is detailed in section 2.1.2.

### **2.1.1** Supervisor interface requirements

The following functions must be implemented by the Supervisor.

- SupCtxInit(): Build the initial context frame on the system stack of the new thread and initialize it's machine dependent thread descriptor SupThreadDesc. The initial values inserted into the context frame on the system stack are used by SupCtxSwitch() when switching to the new thread. SupCtxInit() should build the frame as if the thread is returning from an exception. This function takes the following parameters:

- The system stack bottom, unsigned char \*stackbot.

- Thread parameters descriptor, KnThreadDesc \*threadParams. This descriptor has the entry point of the thread, the thread privilege, priority, the user stack bottom, and the initial execution status. The user stack bottom is used only when the thread is a user thread. In the case of a supervisor thread, this field is ignored.

- Pointer to the thread's machine dependent thread descriptor, SupThreadDesc \*ptThreadDesc.

- Pointer to the virtual address space descriptor of the actor in which the thread will be created, context \*ptContext. Note that context is a class used by the virtual memory system and is not the same as the machine dependent thread context which is basically a set of registers.

SupCtxSwitch(): Switch thread machine dependent context. This function takes the following

parameters:

- Pointer to the old thread, SupThreadDesc\* oldThread

- Pointer to the new thread, SupThreadDesc\* newThread

SupGetUserCtx(): Return a Pointer to a thread's saved context, KnThreadCtx\* SupGetUserCtx(...).

This function takes the following parameter:

- Pointer to the machine dependent thread context descriptor, SupThreadDesc\* desc.

- - Pointer to thread machine dependent context, SupThreadDesc\* desc

- Pointer to exception context frame on the stack, KnThreadCtx\* ctx

- **SupCtxIsUserMod():** Return *true* if thread execution is in User mode else *false*. This function takes the following parameters:

- Pointer to a context frame, KnThreadCtx\* ctx.

- **SupCallConnect():** Connect a vector of handlers to a trap. This function takes the following parameters:

- The trap number, unsigned trapNb

- Pointer to the vector of handlers, KnCallEntry\* hdlVect

- Number of elements in the vector, unsigned NoHdl

- The privilege level unsigned sup. Basically there are two privilege levels: Supervisor and User. If sup is Supervisor in this call then this vector is executed for supervisor actors causing a trap equal to trapNb. If a user Actor causes a trap equal to trapNb, this vector will not be executed unless another SupCallConnect has been explicitly called with the same parameters and sup is set to User.

- **SupCallDisConnect():** Disconnect a Vector of trap handlers. This function takes the following parameters:

- The trap number, unsigned trapNb

- The privilege level, unsigned sup

# **SupItConnect():** Connect a handler to an interrupt. This function takes the following parameters:

• The interrupt number, unsigned intrNb

- The handler to be executed on the interrupt occurrence, KnHdl hdl.

- The privilege level, unsigned sup

**SupItDisconnect():** Disconnect a Interrupt handler. This function takes the following parameters:

- The interrupt number, unsigned intrNb

- The handler to be executed on the interrupt occurrence, KnHdl hdl.

The handler parameter is required since there can be a list of interrupt handlers connected to the interrupt. The (intrNb, hdl) pair uniquely identifies the element to be removed from the list.

SupItLevel(): Return the current interrupt nesting level. This function takes no parameters.

- svMask(): Set the interrupt level. All interrupts equal or less than this level are masked. Returns

previous interrupt level. This function takes the following parameters:

- Interrupt level mask, int intLvlMask.

- svUnMask(): Reset the interrupt level. All interrupts equal or less than this level are unmasked. Returns previous interrupt level. This function takes the following parameters:

- Interrupt level unmask, int intLvlUnMask.

- svMaskAll(): Mask all interrupts. This function has no parameters.

svUnMaskAll(): Unmask all interrupts. This function has no parameters.

- svCopyIn(): copy from User space into kernel space. This function takes the following parameters:

- Source address in user space, char\* src

- Destination address in kernel space, char\* dst

- Size of transfer in bytes, unsigned int count.

- svCopyOut(): copy from Kernel space to User space. This function takes exactly the same parameters as svCopyIn(), only that the source and destination spaces are reversed.

The functions  $sv^*()$  are also part of the Chorus Supervisor actor interface.

**SupTrapConnect():** Connect a handler to a trap. This function takes the following parameters:

- The trap number, unsigned trapNb

- The handler to be executed on the trap occurrence, KnHdl hdl.

SupTrapDisConnect(): Disconnect a Trap handler. This function takes the following parameters:

- The trap number, unsigned trapNb

- The handler to be executed on the trap occurrence, KnHdl hdl.

**SupPanic():** Fatal abort. This function takes no parameters.

SupDebugger(): Call the debugger. This function takes the following parameters:

- The exception context frame pointer, KnThreadCtx\* ctx

- The trap or exception number, unsigned no

**SupPreciseTime():** Return the current precise time. This function takes no parameters.

- SupPutChar(): Write a character on the console device. This is a synchronous operation, i.e., the write returns only after the output is completed. This function takes the following parameters:

- the character to be written, int c

- SupGetChar(): Returns a character from the input device. This is a synchronous operation. This function takes no parameters.

- SupPollChar(): Poll the input device. This function returns 0 if no input is waiting else it returns the character. This function takes no parameters.

In addition to exporting the interface, the *Supervisor* is expected to make up-calls into the kernel upper layers for various synchronous and asynchronous events. The calls are:

- KnDebugEnter(): The Supervisor is expected to call this function to inform the portable layers whenever it enters the debugger. This functions informs the portable layers not to perform context switching when the debugger is entered. This function takes no parameters.

- **KnDebugLeave():** The Supervisor is expected to call this function to inform the portable layers whenever it leaves the debugger. This function takes no parameters.

- KnLock(): Lock the kernel. This function takes no parameters.

- KnUnLock(): Lock the kernel. This function takes no parameters.

- KnHandler(): Exception Handler of the kernel. This function should be called for all unrecoverable exceptions. This function executes the actor specific exception handler if present else calls KnIpcHandler() to abort the thread. This function takes the following parameters:

- Pointer to the exception frame on the stack, KnThreadCtx\* ctx

- Exception number int excNb

- KnItRetSup(): Return from interrupt to supervisor thread. The supervisor after executing the interrupt handlers connected by SupItConnect() prepares to return from the interrupt. This function should be called by the Supervisor if the thread executing at the time of the interrupt was a supervisor thread. This function takes no parameters. A supervisor thread can be preempted only if there is a supervisor thread of higher priority ready to run.

- KnItRetUser(): Return from interrupt to supervisor thread. The supervisor after executing the interrupt handlers connected by SupItConnect() prepares to return from the interrupt. This function should be called by the *Supervisor* if the thread executing at the time of the interrupt was a user thread. This function takes no parameters. This function can cause preemption of the user thread.

- KnAbortHandler(): Abort Handler. If the thread is found to be aborted while returning from an interrupt, then KnAbortHandler() is called. This function takes the following parameters:

- The exception frame on the stack, KnThreadCtx\* ctx as parameter.

- **KnTimeIn():** Record a clock tick. This function should be called by the *Supervisor* every time a clock interrupt occurs. This routine increments the Chorus software clock and executes any routines that have reached their timeout period. This function takes the following parameters:

- The execution mode at the time of the clock interrupt, int supOrUsr.

- The program counter at the time of the clock interrupt, int pc.

# 2.1.2 Supervisor Actor Interface

A portion of the Chorus interface is available only to supervisor actors and would be referred to as the supervisor actor interface. Some of the functions of the supervisor actor interface get directly mapped to corresponding functions of the supervisor interface and the rest of the functions are handled in the portable layers of the Chorus kernel. Ideally, all the calls of the supervisor actor interface except svCheckUserSpace(), svCopy[In/Out](), sv[Un]Mask[All]() are expected to be implemented in the portable layers of the Chorus kernel by calling the appropriate functions in the Supervisor interface. However, due to the way in which instructions are generated on the PA-RISC by the compiler, additional work and portable layer modifications were required to implement this functionality (See section 2.2.9 for details and functionality implementation).

Only those functions of the supervisor actor interface that needed additional implementation are specified below. Note that svCopy[In/Out](), sv[Un]Mask[All]() have already been covered under the *Supervisor* interface.

- svAbortHandler(): Define an abort handler for the Actor. This function takes the following

parameters:

- Actor Capability, KnCap \*actcap.

- Abort Handler, KnHdl routine.

This function is expected to be entirely implemented in the portable layers of the kernel.

- svCallConnect(): Exactly the same function and parameters as SupCallConnect() (see section 2.1.1). This function is expected to be entirely implemented in the portable layers of the kernel.

- svCheckUserSpace(): verify that an address is within the user address space. This function

takes the following parameters:

- the address to be checked, char\* addr.

- This function is expected to be implemented during the port to the target architecture.

- **svExcHandler():** define an exception handler for the Actor. This function takes the following parameters:

- Actor Capability, KnCap \*actcap.

- Exception Handler, KnHdl routine.

This function is expected to be entirely implemented in the portable layers of the kernel.

- svItConnect(): Exactly the same function and parameters as SupItConnect() (see section 2.1.1). This function is expected to be entirely implemented in the portable layers of the kernel.

- svTrapConnect(): Exactly the same function and parameters as SupTrapConnect() (see section 2.1.1). This function is expected to be entirely implemented in the portable layers of the kernel.

- - The routine to be called by kernel on time out, KnToHdl routine.

- The parameter to be passed to routine, void param

- TimeOut period in milliseconds, unsigned int delay.

This function is expected to be entirely implemented in the portable layers of the kernel.

### 2.1.3 Event (Interrupt, Trap and Exception) Handling

The Supervisor is expected to save the register context on the stack, call the appropriate handlers and restore register context when required. The functions in the Supervisor interface that fall in this group are SupTrap[Dis]Connect(), SupIt[Dis]Connect(), SupCall[Dis]Connect(), SupItLevel(), and sv[Un]Mask[All](). The Supervisor implements the data structures and code for these functions and calls the appropriate connected handlers. In the case of interrupts, the Supervisor should execute the list of handlers in the decreasing order of priority and acknowledges the interrupt to the external device raising the interrupt. In all cases, up-calls should be made at the precise points in execution as identified by the supervisor interface. The general algorithms to be used for interrupt, trap, and exception handling are detailed in the Chorus implementation guide [7].

### 2.1.4 Timer and Console Management

The Supervisor manages the timer and console devices. It programs the timer device so that it generates clock ticks at a frequency defined by the K\_CHZ constant defined in **include/chorusConf.h**. Each time a timer interrupt is received, the supervisor calls the **KnTimeIn()** function (see section 2.1.1). The functions of the Supervisor interface that fall under this group are **SupPutChar()**, **SupGetChar()**, **SupPollChar()**.

The Supervisor is responsible for connecting, at least, SupPutChar() and SupGetChar() behind a trap. This trap is used in the implementation of library functions PutChar() and GetChar().

### 2.1.5 Low-level Debugging facility

The Supervisor is responsible for implementing the kernel debugger. The function that implements the debugger is SupDebugger() (see section 2.1.1).

The Supervisor is responsible for connecting the debugger entry point to a trap number. This trap number will be used by the implementation of the **callDebug()** library function. The **callDebug()** function is part of the Chorus kernel interface exported to Chorus Actors.

The Supervisor should call KnDebugEnter() and KnDebugLeave() when entering or leaving the debugger. This avoids context switches when in the debugger.

# 2.1.6 Kernel initialization

The Supervisor implements the function (usually called start()) that performs the kernel initialization. This function performs all the machine dependent and machine independent initialization necessary for calling the portable layers of the kernel. The function start() forms the entry point of the Chorus kernel image. Transfer of control to this entry point is performed by the boot program portion of the boot archive loaded by the resident boot monitor. For more details on the boot archive and Chorus booting procedures see the PA-Chorus booting document[12].

The kernel initialization function is responsible for:

- Initialization of processor specific data like interrupt vector, setting the process status word for appropriate execution mode, etc.

- Static constructors' invocation. Chorus is written in C++, an object oriented language and the static constructors for the various static objects of the kernel must be called.

- Initialization of memory management, by calling VmInit().

- Initialization of various devices and connection of device handlers and trap handlers. This function is embedded in the routine **SupBoardInit()**.

- Calling KnInit(), a function that initializes the portable part of the kernel. This includes scheduler data structure initialization, connection of system call handlers, and creation of the first thread of the system. This first thread is the transformation of the kernel initialization code being executed into a Chorus abstraction. KnInit() returns the new stack pointer to be used by the executing first thread.

- Switching to the new stack pointer and call knMain() which is the main routine of the kernel. knMain() never returns.

# 2.2 Supervisor Implementation

The fundamental data structures KnThreadCtx and SupThreadDesc manipulated by the *Supervisor* code are defined first in sections 2.2.1 and 2.2.2 respectively. This will establish the background to detail the implementation of the *Supervisor* in the rest of the sub-sections.

# 2.2.1 Thread Register Context

The thread register context is basically is the set of general registers and control registers of the processor and any other information that is needed for monitoring, manipulating and resuming the thread at a later stage. The thread register context is required to be typedefined as KnThreadCtx and is declared for PA-RISC in include/PARISC/threadCtx.h. The following are the elements of the KnThreadCtx structure:

• state\_flags, a software register used to track current status of the thread, ex: in-system-call, in-trap, etc.

- General registers gr1,..,gr31. PA-RISC has only 31 32-bit general registers. Gr0 is permanently tied to 0.

- Control registers cr0, cr8,.., cr31. Cr1-cr7 do not exist.

- Instruction space queue tail pcsqe(alias PCSQT), instruction offset queue tail pcoqe(alias PCOQT). These fields contain the address (space and offset) of the next instruction to be executed.

- Kernel stack pointer ksp, this field is a software register. It is 0 when running on the kernel stack and contains the stack pointer to the kernel stack when running on the user stack in user mode.

- Space registers sr0..sr7.

- Floating point registers fr0..fr15.

- Special functional unit status registers, mdhi, mdlo, mdov, keep track of the status of the special functional units, emulated or actual hardware.

The floating point registers and special functional unit fields are ignored in the current implementation. This implies that code having floating point instructions or special function instructions will currently abort. The next version of the implementation will have floating point and special function unit emulation.

# **Discussion** :

The definition of the thread context follows from our design objective of reusing as much of the **Tut** code as possible. The **Tut** project was done in two phases. First the HP-UX virtual memory system was replaced by Mach virtual memory system. In the second phase, HP-UX was modified to provide the mach thread abstraction and interface. In the case of the **Tut** kernel with threads, there are 3 different structures used to store the thread context depending on the execution mode of the thread and the purpose of accessing the context.

The purpose of each of the structures of the **Tut** kernel is given below:

- save\_state structure is used when the thread enters the kernel mode through system calls, traps and interrupts.

- PCB structure is used when the thread was executing in kernel mode.

- hppa\_thread\_state structure is the context visible to the user for interrogation and modification.

In the case of Chorus, the machine independent layers recognize only one structure for the thread context, i.e., KnThreadCtx. For the PA-Chorus port, we defined KnThreadCtx structure as the union of the three structures. This enabled us to use the same structure uniformly through out the kernel and allowed us to use the low-level **Tut** code for the system-call interface, interrupt and trap handling as our starting point and make the Chorus specific modifications relatively easily. Further, we saw no reason to have distinct structures as a single structure can be used to store different levels and types of information.

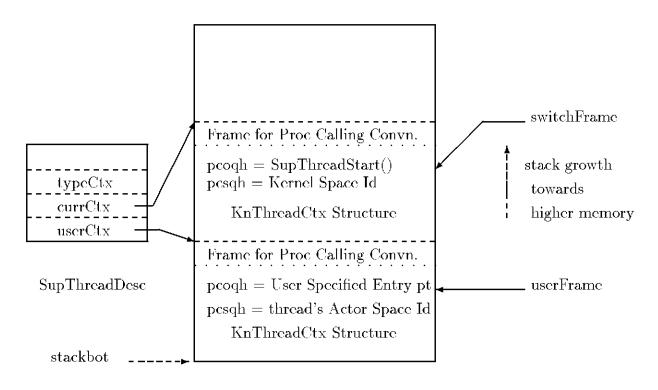

Figure 4: Machine dependent thread descriptor: SupThreadDesc

### 2.2.2 Machine Dependent Thread Descriptor

The machine dependent thread descriptor is typedefined as SupThreadDesc. As described in section 2.1, this descriptor is used to keep track of the thread's system stack, user stack and the thread's context. In the case of PA-RISC, SupThreadDesc is defined in include/PARISC/sv.h as in fig 4.

The fields of SupThreadDesc, except the link field, get initialized in SupCtxInit() (see section 2.2.3), and remain fixed during the life time of the thread.

### 2.2.3 SupCtxInit()

This function is implemented in kern/PARISC/sv.cxx. The initialization of the new thread is performed in the following manner:

- 1. If the thread is the first thread of the kernel then exit from the function. The first thread of the kernel is nothing but the kernel initialization code being made part of the thread abstraction and recognizable by the Chorus portable layers. This thread ultimately becomes the idle thread of the system. Since this "thread" was already executing before it was created, there is nothing to be done at this stage. The machine dependent initialization for the first thread would have been already performed in **start()** in **kern/PARISC/sv.cxx** during kernel initialization.

- 2. Force the allocation of the system stack of the thread. At the point of calling SupCtxInit(), the system stack of the new thread is mapped, but physical memory is not allocated, by the virtual memory layers. It is necessary for the system stack to be actually allocated in physical memory before starting up the new thread since traps caused by the new thread must be handled on its system stack and this would cause recursive traps if the system stack is not physically allocated.

- 3. Allocate two frames of type KnThreadCtx\*: userFrame and switchFrame on the system stack (see fig 5).

- 4. Initialize the userFrame as follows:

- (a) If the thread is a user thread then initialize the stack pointer as follows:

$userFrame \rightarrow sp = threadParams \rightarrow sp + FM_SIZE.$

FM\_SIZE is the frame size needed to satisfy the PA-RISC procedure calling conventions.

(b) If the thread is a supervisor thread then initialize the stack pointer as follows:

$\begin{aligned} \texttt{fr\_size} &= \texttt{sizeof}(\texttt{KnThreadCtx}) + \texttt{FM\_SIZE} + \texttt{FM\_FIXED\_ARG\_SIZE}. \\ \texttt{userFrame} \rightarrow \texttt{sp} &= \texttt{stackbot} + 2 * \texttt{fr\_size}. \end{aligned}$

The FM\* operands above are needed to satisfy the PA-RISC procedure calling conventions.

(c) Initialize the thread's Processor Status Word. As mentioned earlier, the thread frame should be initialized as if the thread is returning from exception. So the required *inter-ruption* parameter registers are updated as follow:

```

userFrame \rightarrow ipsw = Q + C + D + I,

userFrame \rightarrow eiem = Enable-all-interrupts

```

(d) Initialize the thread's protection identity registers as follows:

```

userFrame\rightarrowpid1 = 0,

userFrame\rightarrowpid3 = 0,

userFrame\rightarrowpid4 = 0,

userFrame\rightarrowpid2 = Protection Id of the Actor's context.

```

(e) Initialize the thread's space registers and the instruction address queues as follows:

```

userFrame→sr4 = spaceId of thread's Actor,

userFrame→sr5 = spaceId of thread's Actor,

userFrame→pcsqh = spaceId of thread's Actor,

userFrame→pcsqt = spaceId of thread's Actor,

userFrame→sr6 = KernelSpaceID.

userFrame→sr7 = KernelSpaceID.

userFrame→pcoqh = threadParams→pc,

userFrame→pcoqt = userFrame→pcoqh + Instruction length (4 bytes).

```

- (f) Initialization of the data pointer (dp) of the thread is performed as follows:

- i. If the thread is a kernel thread then set dp as follows:

$userFrame \rightarrow dp = data_pointer$  (the kernel's data pointer).

- ii. If the thread belongs to a user Actor then set dp as follows:

userFrame→dp = 0x40000000 (the absolute virtual address of a user Actor's data pointer).

- iii. If the thread is not the first thread of the supervisor actor then initialize the dp from the datapointer value in the saved context of the first thread of the supervisor actor. This value can be found by looking at the thread list attached to the thread's actor.

- iv. If none of the above cases is true, then do nothing to initialize the dp. This is the case when the new thread is the first thread of the supervisor actor. Since this thread is the main thread of the actor, the start up sequence will be similar to a unix process, i.e., the execution starts at an entry point in a crt0.0 equivalent and then branches to main() after some initialization. The dp in this case would be set by the code in crt0.0. The code for the crt0.0 equivalent is in **ktests/PARISC/kt\_ass.s**.

It is important for the dp to be set before any part of the main program gets executed since instructions produced by the compiler are generated with respect to the dp.

- 5. The variable switchFrame points to the frame that is equivalent to a context frame saved by the scheduler during a context switch operation. The fields are initialized such that on a context switch to the new thread, control is transferred to the kernel procedure SupThread-Start() which executes in privileged mode without preemption. SupThreadStart() is implemented in kern/PARISC/supctx.s. This routine loads the values from the userFrame portion of the system stack and performs a return from exception sequence to transfer control to the new thread's actual entry point. The return from exception sequence is described in section 2.2.11. The frame pointed by switchFrame is initialized as follows:

- (a) Initialize the Processor status word as follows:

- switchFrame $\rightarrow$ ipsw = Q + C + D, Note that Interrupts are not enabled.

- (b) Initialize the data pointer dp to the kernel's data pointer:

$switchFrame \rightarrow dp = data_pointer$

(c) Initialize the space registers:

$switchFrame \rightarrow sr4 = KernelSpaceId;$  $switchFrame \rightarrow sr5 = KernelSpaceId;$  $switchFrame \rightarrow sr6 = KernelSpaceId;$  $switchFrame \rightarrow sr7 = KernelSpaceId;$

(d) Initialize the instruction address queues:

switchFrame pcsqh = KernelSpaceId; switchFrame pcsqt = KernelSpaceId; switchFrame pcoqh = SupThreadStart, switchFrame pcoqt = SupThreadStart + Instruction length (4 bytes).

- 6. Thread descriptor ptThreadDesc fields are initialized as follows:

- (a) typeCtx = privilege value passed in threadParams.

- (b) currCtx = stackbot + 2 \* fr\_size.

- (c) userCtx = stackbot + fr\_size.

### **Discussion** :

Note that to change a value in the switchFrame, we have to subtract fr\_size bytes from currCtx and then use the resultant address as KnThreadCtx\*. The same argument is true for the userFrame. The pointers currCtx and userCtx are fixed for the life time of the thread. There is an inefficiency in space usage and time of access to the context by this definition. First, 2\*fr\_size bytes are lost in the system stack. To access a register in the current context, one has to first get the context pointer from the context pointed to by currCtx and then access the register. This would not have been necessary if currCtx was not fixed but pointed directly to the current context. The advantage of the current approach is in debugging. Since the currCtx is always available at a fixed position relative to the bottom of the system stack, it offers an easy way of looking up the current context of the thread during memory dumps.

The initialization of the dp is complicated by the fact that the dp is not always available to the kernel at the time of performing the machine dependent initialization.

This is a consequence of the fact that we did not have a data pointer field as part of the machine dependent context mmuContext. Having a dp field in the class mmuContext works fine as long as

Thread's system stack

Figure 5: Machine dependent Thread Initialization

there is one executable image per virtual address space. In the case of Chorus all supervisor actors, which are independent executable images, share the same context, i.e., KernelContext. In such a case, it is no longer sufficient to have one dp field per mmuContext. One solution to simplifying the initialization code for dp is to have a dp in the actor and have this field initialized during the startup sequence of the main thread of the actor. Then for all the threads created then onwards in this actor, this field can be used to initialize the dp in their startup thread context. Note that in this case, a thread of actor A cannot create any other thread other than the main thread of actor B unless the main thread of actor B has already executed its startup sequence and initialized it's actor specific dp. The most elegant solution would be to do the dp initialization at the time of creating an actor. But there is no clear way of initializing the data pointer of an actor in the portable layers.

# 2.2.4 SupCtxSwitch()

**SupCtxSwitch()**, the thread machine dependent context switch function, is implemented in **kern/PARISC/supctx.s**. This function performs the switch in the following manner<sup>7</sup>.

1. Allocate a fr\_size frame on the system stack of the old thread from the current stack pointer. Save general registers including the current sp and thread specific control registers. The return address of SupCtxSwitch() becomes the new point of resumption for the oldThread. This implies that when a context switch loads back the old thread, it will be as though it has returned from SupCtxSwitch(). To achieve this pcoqh and pcoqt are set to RP and RP+4

<sup>&</sup>lt;sup>7</sup>Note that oldThread is really the running thread and the purpose of SupCtxSwitch() is to save the register context of the running thread and switch to the new thread

respectively. Update the stack pointer value in the fixed switch Frame pointed to by currCtx  $^8\cdot$

2. Find the position of the save context frame from the stack pointer field in the fixed context frame pointed to by newThread→currCtx. Restore general registers and some control registers. Perform a return from exception sequence (see step ( 3f) of trap handling) to set the instruction queue registers and the process status word.

# **Discussion** :

Doing a return from exception sequence is not necessary to implement the context switch. An alternate way is to do a procedure call return into the context of the new thread (the thread to be scheduled). This can be achieved by performing a branch to the value in the RP of the context of the new thread. The reason the return from exception sequence was chosen is to have more control over the PSW bits during debugging. The PSW bits can be changed in the saved context of the blocked thread and thus enable any debug traps if required. The disadvantage is the inefficiency in this method of implementation due to the greater number of operations that need to be performed.

# 2.2.5 SupGetUserCtx()

This function is implemented in kern/PARISC/sv.h.

# 2.2.6 SupCtxReset()

This function is implemented in kern/PARISC/sv.cxx. The function blindly overwrites the context frame on the stack by the user context frame portion of the SupThreadDesc.

# Discussion :

This function needs to be changed to perform some sanity and protection checks before modifying the thread context.

# 2.2.7 SupCtxIsUserMod()

This function is implemented in kern/PARISC/sv.h. The function returns *true* if the sr4 of the context is not the same as the kernel's space id. Other wise it returns false.

# **Discussion** :

One of the experiments which we want to do is to take the supervisor actors from the same space as the kernel and use the multiple privilege levels. One of the interesting aspects of the architecture is the cheap mechanism for system calls and the multiple privilege levels. This function would definitely break if such a separation is done.

<sup>&</sup>lt;sup>8</sup>Actually currCtx points to the top of the switchFrame. Therefore, fr\_size bytes have to be subtracted from currCtx before accessing a field in the KnThreadCtx structure portion of the switchFrame

### 2.2.8 The various connect and disconnect functions

This section details the implementation of SupCall[Dis]Connect(), SupIt[Dis]Connect() and SupTrap[Dis]Connect(). These three pairs of functions are implemented in svConnect.cxx in the directory kern/PARISC.

These functions are provided by Chorus so that the portable layers of the Chorus kernel can attach handlers to traps, interrupts, system calls in a machine independent manner. The chorus kernel maps the **Connect()** system calls provided to supervisor actors to the corresponding **Connect()** calls of the *Supervisor* interface. We found that we needed to have more information than the specified parameters for the **Connect()** calls to satisfy the system call interface for supervisor actors. This problem is discussed in detail in section 2.2.9. In this section, we will discuss the different semantics that apply to some of the parameters to these **\*Connect()** calls on PA-RISC in contrast to what Chorus originally envisaged. The semantic differences are as follows:

- The Chorus interface expects the first parameter to **SupCallConnect()** and **SupTrapConnect()** to be a trap number. **SupCallConnect()** is used in the Chorus kernel to connect a vector of handlers behind a trap. In the case of implementing UNIX as a collection of actors (sub-system), a SupCallConnect() is made from the sub-system actor called the PM to connect a vector of system call routines behind a specified trap number to handle UNIX system calls. In the case of PA-RISC, it is not necessary to cause a trap to perform a system call. There is an efficient qateway mechanism (see section 4) by which a controlled transfer between privilege levels can be achieved. This method is the proper mechanism for making system calls on this architecture (HP-UX and MPE use the same approach) and has been used in the implementation of system calls for PA-Chorus. The consequence is that calling the first parameter to SupCallConnect() as trapNb is not quite correct. Since the purpose of having SupCallConnect() and SupTrapConnect() is to build sub-systems (including Chorus as the base case), this number is distingushed in the Supervisor layer as a real hardware trap number or a *sub-system* number to which a vector of handlers (Sup-**CallConnect()**) or a single handler (**SupTrapConnect()**) should be connected. Hence an appropriate name for the first parameter would be subSysOrTrapNb. Additional constants were added in **include/PARISC/syscall.h** to map symbolic constants for sub-systems to numbers. For example: CHORUS\_SUBSYS is defined to be 31. The range of hardware trap numbers does not overlap with the range of sub-system numbers possible. This makes differentiation between a sub-system number and a trap number simple.

- The Chorus interface expects the first parameter to **SupItConnect()** to be a hardware interrupt number. In the case of PA-RISC, all the external devices including the clock raise the same interrupt #4 (External Interrupt). We found it more elegant to pass the number of the external device as a parameter to SupItConnect() rather than the interrupt number. For example: To connect clock and disk handlers, two calls SupItConnect(CLOCK, clockIIdl, clock-prio), SupItConnect(DISK01, diskIIdl, disk01prio) are required. The interface is not changed, only the meaning of the first parameter is slightly different. However, it is possible to connect all the device handlers to the external interrupt #4. Hence an appropriate name for the first parameter would be DeviceOrIntrNb. An include file include/PARISC/extern\_intr.h was created to map symbolic constants for devices to mapped to integers. The numbers possible for hardware interrupts do not overlap with that of the devices. This makes differentiation between a device number and a interrupt number simple.

The basic data structures that have been used for the implementation are presented in figure 6.

```

typedef struct {

unsigned long

/* No of functions in the array being connected */

funcNb;

KnCallEntry*

/* address of the array */

calls;

} vector_desc;

typedef struct {

connectType;

unsigned int

/* Array or function connected */

union {

vector_desc vector;

KnHdl

hdl;

};

VmAddr

/* The $global$ of the Supervisor Actor */

dataPointer;

} supCallTbl;

/* MAX_SYS_NUM = 25 from include/PARISC/syscall.h; the maximum number *

* of sub-systems that can simultaneously run on top of Chorus

*/

supCallTbl userTrapVect[MAX_SYS_NUM]; /* For User Actor System Calls */

supCallTbl kernTrapVect[MAX_SYS_NUM]; /* For Sup Actor System Calls */

```

Figure 6: Data structures for System Call Handling

- The structures userTrapVect and kernTrapVect are used by SupCallConnect(), Sup-TrapConnect().SupCallHandler() finds and executes the routine attached by the Connect() calls during system call execution.

- vect, DeviceVect are updated by SupItConnect() and SupTrapConnect(). The routines attached to the various interrupts and traps by the Connect() calls are executed by SupItHandler(),SupItSelector() or SupTrapHandler() on the occurrence of the those interruptions. The data structures for interruption handling are presented in figure 7. In addition to the 25 PA-RISC interruptions, there are 3 psuedo-interruptions generated by the low-level event handling layers. Therefore, we maintain an INTRMAX element array (25+3 elements) and allow handlers to be attached to one single vector vect. Currently the psuedo-interruptions are handled in the kernel itself.

PA-RISC has one external interrupt for all external devices including the ITMR. This implies that all handlers for different external devices would have to be connected to the same position in vect. To avoid this, DeviceVect is introduced to keep the interrupt handlers device-specific rather than connecting all the device handlers to one position in the vect array.

The implementation of the various **Connect()** calls is now presented:

SupItConnect(itNum, hdl) : calls SupItConnectParisc() with kernel's \$global\$ as additional parameter. SupItConnectParisc() allocates a itLink structure from the itPool, stores the parameters of the function in the structure and attaches it to vect or DeviceVect depending on the actual interrupt number parameter (itNum) being a PA-RISC interrupt number or a symbolic device name. Two or more handlers for the same interrupt or device are linked in descending order of priority.

```

typedef struct {

itLink* lnk:

KnHdl routine;

unsigned long priority;

VmAddr dataPointer;

} itLink:

typedef struct {

KnHdl routine;

VmAddr dataPointer;

} KnHdlEntry;

typedef union {

itLink* lnk;

KnHdlEntry hdlEnt;

} VectEntry;

VectEntry vect[INTRMAX];

VectEntry DeviceVect[NumOfExternalDevices]

```

Figure 7: Data Structures for Interruption handling

The advantage of having a separate table for external devices is for efficiency of search during interrupt handling.

SupTrapConnect(trapOrSubSysNum, hdl) : calls SupTrapConnectParisc() with the kernel's \$global\$ as an additional parameter. SupItConnectParisc() does the following:

- If trapOrSubSysNum is a PA-RISC trap, then store the dataPointer and hdl at vect[trapOrSubSysNum].

- If trapOrSubSysNum is sub-system number, then this implies a single routine interface for system calls in contrast to a vector of handlers connected by **SupCallConnect()**. Update both userTrapVect and kernTrapVect by the same parameters and update connectType to be FUNC\_TYPE.

- If neither of the above condition holds, then return illegal value status.

As explained in the beginning of this section, it is not necessary to cause a trap to perform a system call on this architecture. If a sub-system manager requires a single routine to handle all the system calls instead of a vector of handlers, there are now two ways of doing it:

- SupTrapConnect() with subsystem number instead of trap number as first parameter and the handler as second parameter. This is the interface used by the UNIX sub-system implementation to provide UNIX system call services to the actors of the sub-system.

- SupCallConnect() with size of the array equal to one. In this case the stub library should always have the system call number equal to 1, and the single handler in vectorOfHandlers responsible for distingushing various system calls of the actors running on that sub-system.

- SupCallConnect(no, vectorOfHandlers, NoHdl, privilege) : calls SupCallConnectParisc()

with the kernel's \$global\$ as an additional parameter. SupCallConnectParisc() connects

the vectorOfHandlers to userTrapVect[no] if privilage is User or to kernTrapVect[no]

if privilage is Supervisor. The connectType is set to VECTOR\_TYPE.

- **DisConnect functions** : All the disconnect functions are straight forward and basically reset the corresponding locations to NULL or deallocate the allocated structure as in the case of interrupts.

# 2.2.9 Supervisor Actor Interface Implementation