## **Portland State University**

# **PDXScholar**

**Dissertations and Theses**

**Dissertations and Theses**

Spring 6-10-2013

# Equivalence Checking for High-Assurance Behavioral Synthesis

Kecheng Hao

Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Hardware Systems Commons, and the Other Computer Sciences Commons

Let us know how access to this document benefits you.

#### Recommended Citation

Hao, Kecheng, "Equivalence Checking for High-Assurance Behavioral Synthesis" (2013). *Dissertations and Theses*. Paper 1066.

https://doi.org/10.15760/etd.1066

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

# Equivalence Checking for High-Assurance Behavioral Synthesis

by

# Kecheng Hao

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

Dissertation Committee:

Fei Xie, Chair

Feng Liu

Sandip Ray

Bryant York

Fu Li

Portland State University 2013

#### ABSTRACT

The rapidly increasing complexities of hardware designs are forcing design methodologies and tools to move to the Electronic System Level (ESL), a higher abstraction level with better productivity than the state-of-the-art Register Transfer Level (RTL). Behavioral synthesis, which automatically synthesizes ESL behavioral specifications to RTL implementations, plays a central role in this transition. However, since behavioral synthesis is a complex and error-prone translation process, the lack of designers' confidence in its correctness becomes a major barrier to its wide adoption. Therefore, techniques for establishing equivalence between an ESL specification and its synthesized RTL implementation are critical to bring behavioral synthesis into practice.

The major research challenge to equivalence checking for behavioral synthesis is the significant semantic gap between ESL and RTL. The semantics of ESL involve untimed, sequential execution; however, the semantics of RTL involve timed, concurrent execution. We propose a sequential equivalence checking (SEC) framework for certifying a behavioral synthesis flow, which exploits information on successive intermediate design representations produced by the synthesis flow to bridge the semantic gap. In particular, the intermediate design representation after scheduling and pipelining transformations permits effective correspondence of internal operations between this design representation and the synthesized RTL implementation, enabling scalable, compositional equivalence checking. Certifications of loop and

function pipelining transformations are possible by a combination of theorem proving and SEC through exploiting pipeline generation information from the synthesis flow (e.g., the iteration interval of a generated pipeline). The complexity brought by bubbles in function pipelines is creatively reduced by symbolically encoding all possible bubble insertions in one pipelined design representation. The result of this dissertation is a robust, practical, and scalable framework for certifying RTL designs synthesized from ESL specifications. We have validated the robustness, practicality, and scalability of our approach on industrial-scale ESL designs that result in tens of thousands of lines of RTL implementations.

# DEDICATION

To my parents, Fengming and Fanying

To my wife, Kai

To my daughter, Sophia

#### ACKNOWLEDGMENTS

It has been a long journey to finish this dissertation research. During my research, I got help from many people, including my teachers, collaborators, friends, and family, therefore I would like to take this opportunity to thank all of them.

First and foremost, I wish to express my thanks and great appreciation to my advisor Prof. Fei Xie for his patient guidance, enthusiastic encouragement and useful critiques. He is a wonderful advisor. He guided me to learn how to identify critical problems and resolve them, which is invaluable to my research. He is also an amazing researcher. His rare combination of strengths in both the practical and the theoretical has been a continuous inspiration to me. Without his help, I do not believe I can accomplish this dissertation.

I would also like to thank Dr. Sandip Ray for his enormous amount of time and effort that he spent on my research. All my papers related to this dissertation are finished by collaborating with Sandip. He is a great collaborator and an outstanding researcher. He has always helped me with my research through email and phone, even in weekends. My thanks to Dr. Jin Yang and Dr. Naren Narasimhan for generously providing feedback and discussing future work from an industrial point of view.

I am grateful to my other committee members, Prof. Fu Li, Prof. Feng Liu, and Prof. Bryant W. York, for inspiration in many ways and valuable feedback on my research proposal and dissertation. Thank Prof. Xiaoyu Song, who initially brought me on board to electronic design automation.

The dissertation also benefits from various discussion with from current and former lab members: Yan Chen, Ping Hang Cheung, Nicholas T. Pilkington, Juncao Li, Sharookh Daruwalla, Zhenkun Yang, and Disha Gandhi. I also would like to thank my colleagues at Xilinx for exchanging knowledge of high-level synthesis, including Dr. Yiping Fan, Dr. Zhiru Zhang, Dr. Peichen Pan, and Dr. Guoling Han.

Finally, I must acknowledge my family for supporting me all the time. Thank you to my parents for always being supportive. Especially thanks to my lovely wife, Kai, for her love, patience, encouragement, and immense personal sacrifice.

# TABLE OF CONTENTS

| Abstra  | ıct                                                        |

|---------|------------------------------------------------------------|

| Dedica  | ition                                                      |

| Ackno   | $f wledgments \ \ldots \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ |

| List of | Tables                                                     |

| List of | Figures                                                    |

| Chapte  |                                                            |

| 1.1     | Motivation and Problem Statement                           |

|         | 1.1.1 Motivation                                           |

|         | 1.1.2 Problem Statement                                    |

| 1.2     | Contribution                                               |

| 1.3     | Related Work                                               |

| 1.4     | Dissertation Outline                                       |

| Chapte  | er 2 BACKGROUND                                            |

| 2.1     | Behavioral Synthesis                                       |

| 2.2     | Solver Technology                                          |

|         | 2.2.1 Binary Decision Diagram                              |

|         | 2.2.2 Boolean Satisfiability Problem                       |

|         | 2.2.3 Satisfiability Modulo Theories                       |

| 2.3     | Scalable Verification Techniques                           |

|         | 2.3.1 Symbolic Simulation                                  |

|         | 2.3.2 Equivalence Checking for Logic Synthesis             |

| Chapte  | er 3 EQUIVALENCE CHECKING                                  |

| 3.1     | Clocked Control/Data Flow Graphs                           |

| 3.2     | Circuit Model                                              |

| 3.3     | Correspondence between CCDFGs and Circuits 2               |

| 3.4                                       | Dual-Rail Simulation for Equivalence Checking                                                                                                                                                                                                                                                                                                                              | 23                                                 |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 3.5                                       | Tool Implementation                                                                                                                                                                                                                                                                                                                                                        | 25                                                 |

| 3.6                                       | Experimental Results                                                                                                                                                                                                                                                                                                                                                       | 27                                                 |

| Chapte                                    | er 4 OPTIMIZATIONS                                                                                                                                                                                                                                                                                                                                                         | 29                                                 |

| 4.1                                       | Motivation and Overview                                                                                                                                                                                                                                                                                                                                                    | 29                                                 |

| 4.2                                       | Cut-points                                                                                                                                                                                                                                                                                                                                                                 | 29                                                 |

| 4.3                                       | Cut-loop Optimization                                                                                                                                                                                                                                                                                                                                                      | 30                                                 |

| 4.4                                       | Modular Analysis                                                                                                                                                                                                                                                                                                                                                           | 33                                                 |

| 4.5                                       | Experimental Results                                                                                                                                                                                                                                                                                                                                                       | 35                                                 |

| Chapte                                    | er 5 SEC FOR SYNTHESIZED LOOP PIPELINES                                                                                                                                                                                                                                                                                                                                    | 38                                                 |

| 5.1                                       | Motivation and Overview                                                                                                                                                                                                                                                                                                                                                    | 38                                                 |

| 5.2                                       | Challenges with Loop Pipelines                                                                                                                                                                                                                                                                                                                                             | 38                                                 |

| 5.3                                       | SEC with Reference Model                                                                                                                                                                                                                                                                                                                                                   | 40                                                 |

| 5.4                                       | Experimental Results                                                                                                                                                                                                                                                                                                                                                       | 49                                                 |

|                                           |                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

| Chapte                                    |                                                                                                                                                                                                                                                                                                                                                                            | <b>5</b> ]                                         |

| Chapte 6.1                                |                                                                                                                                                                                                                                                                                                                                                                            | <b>5</b> 1                                         |

| -                                         | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES .                                                                                                                                                                                                                                                                                                                              |                                                    |

| 6.1                                       | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES .  Motivation and Overview                                                                                                                                                                                                                                                                                                     | 5                                                  |

| 6.1<br>6.2                                | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES .  Motivation and Overview                                                                                                                                                                                                                                                                                                     | 53<br>53                                           |

| 6.1<br>6.2                                | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES .  Motivation and Overview                                                                                                                                                                                                                                                                                                     | 53<br>53<br>55                                     |

| 6.1<br>6.2                                | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES .  Motivation and Overview                                                                                                                                                                                                                                                                                                     | 5;<br>5;<br>5;                                     |

| 6.1<br>6.2<br>6.3                         | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES .  Motivation and Overview                                                                                                                                                                                                                                                                                                     | 51<br>53<br>55<br>57<br>70                         |

| 6.1<br>6.2<br>6.3                         | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES  Motivation and Overview                                                                                                                                                                                                                                                                                                       | 51<br>53<br>55<br>57<br>70<br>71                   |

| 6.1<br>6.2<br>6.3<br>6.4<br>Chapte        | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES  Motivation and Overview  Challenges with Function Pipelining  SEC for Function Pipelining  6.3.1 Algorithm to build Reference Model  6.3.2 SEC between CCDFGs and the RTL  Experimental Results  er 7 CONCLUSION AND FUTURE WORK                                                                                              | 51<br>53<br>55<br>57<br>70<br>71                   |

| 6.1<br>6.2<br>6.3<br>6.4<br>Chapte<br>7.1 | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES  Motivation and Overview                                                                                                                                                                                                                                                                                                       | 51<br>55<br>55<br>70<br>71<br><b>7</b> 4           |

| 6.1<br>6.2<br>6.3<br>6.4<br>Chapte<br>7.1 | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES  Motivation and Overview  Challenges with Function Pipelining  SEC for Function Pipelining  6.3.1 Algorithm to build Reference Model  6.3.2 SEC between CCDFGs and the RTL  Experimental Results  er 7 CONCLUSION AND FUTURE WORK  Summary of Contributions  Future Research Directions                                        | 51<br>55<br>55<br>57<br>70<br>71<br>74<br>74       |

| 6.1<br>6.2<br>6.3<br>6.4<br>Chapte<br>7.1 | er 6 SEC FOR SYNTHESIZED FUNCTION PIPELINES  Motivation and Overview  Challenges with Function Pipelining  SEC for Function Pipelining  6.3.1 Algorithm to build Reference Model  6.3.2 SEC between CCDFGs and the RTL  Experimental Results  er 7 CONCLUSION AND FUTURE WORK  Summary of Contributions  Future Research Directions  7.2.1 Hierarchical Function Pipelines | 51<br>51<br>51<br>51<br>71<br>71<br>71<br>71<br>71 |

# LIST OF TABLES

| 3.1 | Bit-level equivalence checking statistics  | 27 |

|-----|--------------------------------------------|----|

| 3.2 | Word-level equivalence checking statistics | 28 |

|     | Designs, features, and optimizations       |    |

| 4.2 | Word-level equivalence checking statistics | 36 |

| 5.1 | Loop pipelining experimental results       | 50 |

| 6.1 | Function fipelining experimental results   | 73 |

# LIST OF FIGURES

| 2.1 | Input and output of behavioral synthesis                           | 10 |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Decision tree representation                                       | 12 |

| 2.3 | BDD transformations                                                | 13 |

| 2.4 | Simple cut-point example                                           | 18 |

| 3.1 | CCDFGs for the TEA encryption function                             | 20 |

| 3.2 | Operation mapping between CCDFG and circuit                        | 22 |

| 3.3 | Dual-rail simulation scheme for equivalence checking between CCDFG |    |

|     | and circuit                                                        | 24 |

| 3.4 | Framework of equivalence checker                                   | 26 |

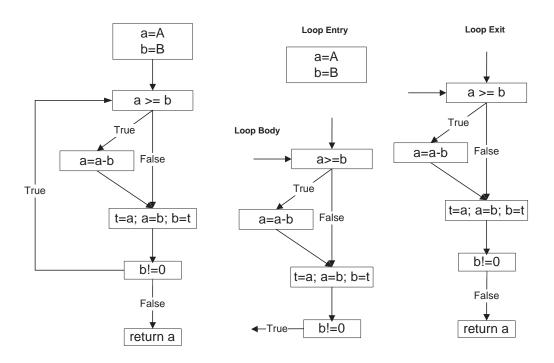

| 4.1 | C source code and CCDFG for GCD                                    | 31 |

| 4.2 | Cut-loop optimization for GCD example                              | 32 |

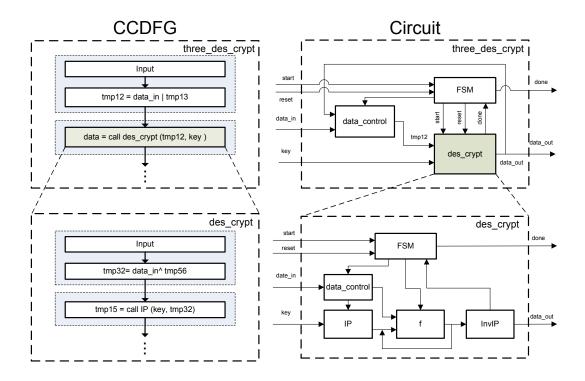

| 4.3 | Modular SEC for 3DES                                               | 33 |

| 5.1 | Example of loop pipeline                                           | 39 |

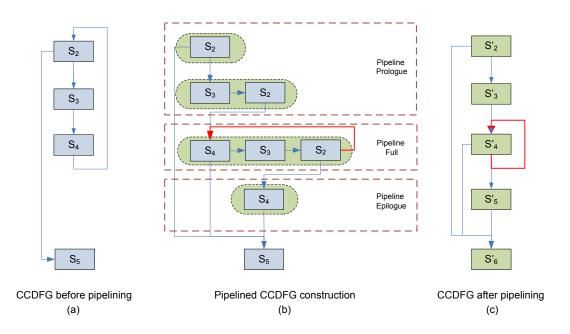

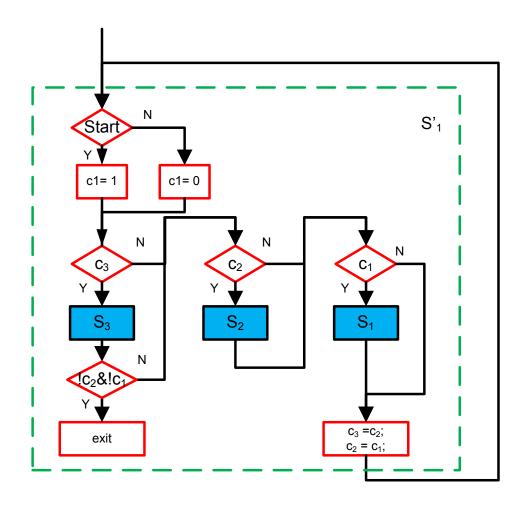

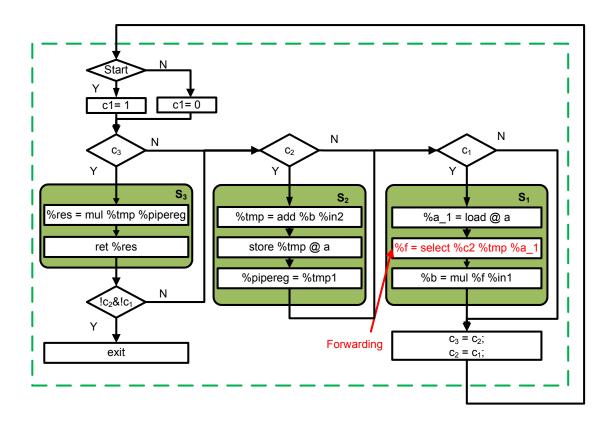

| 5.2 | Input and output CCDFGs of loop pipelining transformation          | 42 |

| 5.3 | Construction of scheduling steps                                   | 44 |

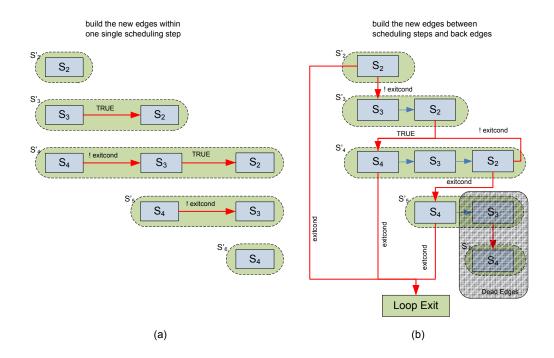

| 5.4 | Construction of edges                                              | 45 |

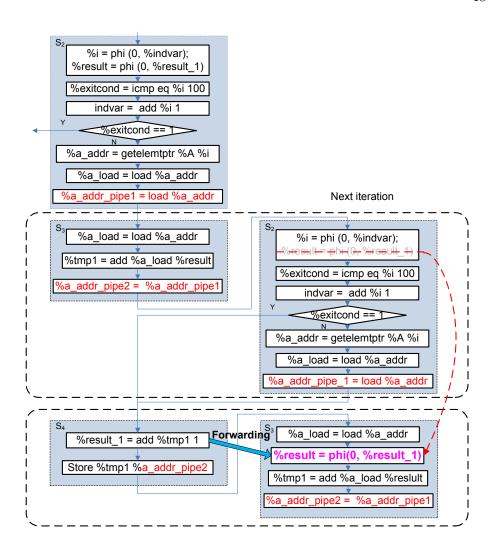

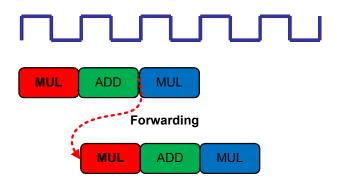

| 5.5 | Pipeline registers and forwarding                                  | 48 |

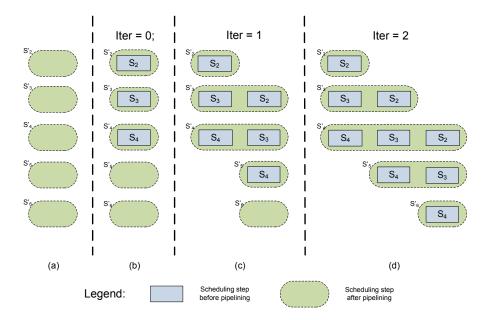

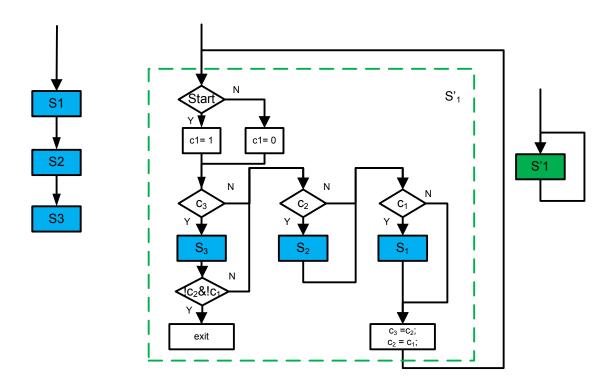

| 6.1 | Example of function pipeline                                       | 52 |

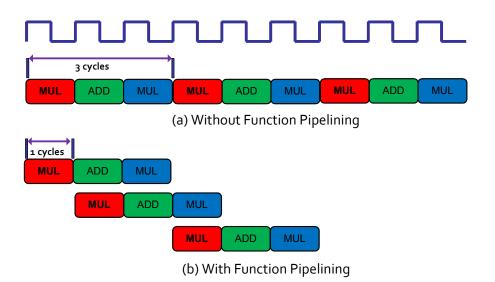

| 6.2 | Difference between un-pipelined version and pipelined version      | 53 |

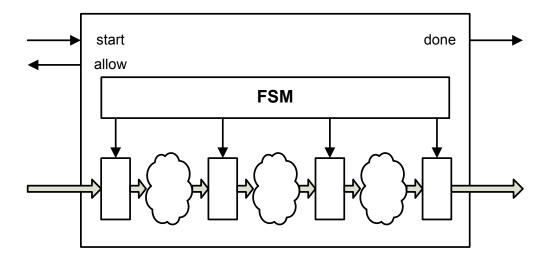

| 6.3 | Hardware interface                                                 | 54 |

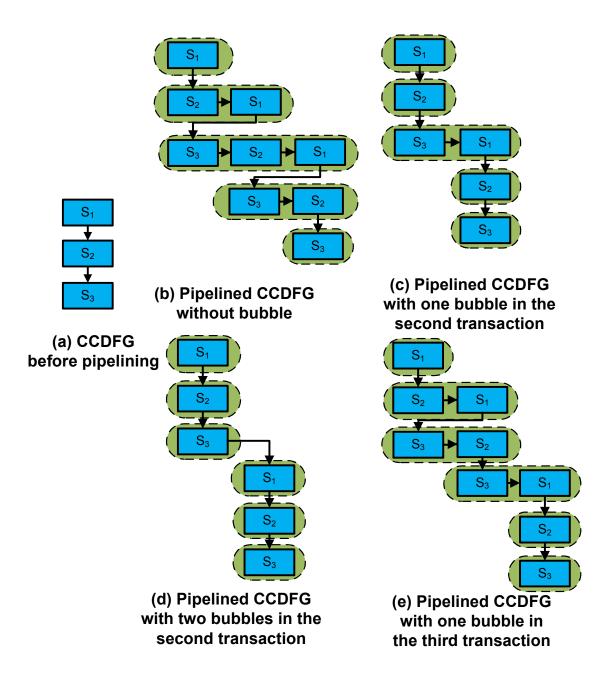

| 6.4 | Pipelined CCDFGs for different bubble insertion scenarios          | 56 |

| 6.5 | Input and output CCDFGs of function pipelining transformation      | 59 |

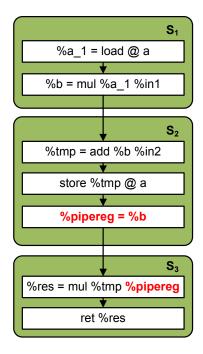

| 6.6 | Generate pipeline registers                                        | 61 |

| 6.7 | Construction of scheduling steps and edges                         | 64 |

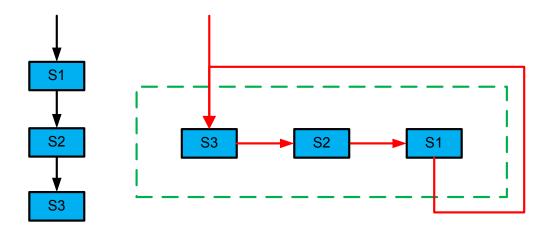

| 6.8 | Insert guard variables and assignment                              | 65 |

| 6.9 | Final pipelined CCDFG                                              | 68 |

|     |                                                                    |    |

| 6.10 | Waveform of | of p | ipeline | forwarding |  |  |  |  |  |  |  |  | 6 | ;9 |

|------|-------------|------|---------|------------|--|--|--|--|--|--|--|--|---|----|

|      |             |      |         |            |  |  |  |  |  |  |  |  |   |    |

#### Chapter 1

#### INTRODUCTION

#### 1.1 MOTIVATION AND PROBLEM STATEMENT

#### 1.1.1 Motivation

Recent years have seen increasingly higher complexities in hardware designs, resulting from advances in VLSI technology as well as growing demands on performance and power imposed by modern applications. Such complexities, in addition to stringent time-to-market requirements, make it challenging to develop reliable, high-quality systems through hand-crafted Register Transfer Level (RTL) implementations. This underlines the needs for modeling, synthesis, and validation of hardware at higher levels of abstraction and has motivated a gradual migration away from RTL towards Electronic System Level (ESL) which allows design functionality to be described abstractly in high-level languages such as SystemC or C/C++. However, practicality of ESL designs crucially depends on reliable tools for behavioral synthesis, that is, automated synthesis of a hardware circuit from its ESL description. Behavioral synthesis tools apply a sequence of transformations to compile the behavioral description to an RTL implementation.

Several behavioral synthesis tools are available today, e.g., AutoESL [72], CatapultC [54], C-to-Silicon [11], Cynthesizer [23], Spark [25], and LegUp [13]. Nevertheless, and despite a great need, behavioral synthesis has not yet found wide acceptance in current industrial practice. A major barrier to its adoption is the

lack of designers' confidence in correctness of synthesis tools themselves. The large semantic gap between a synthesized implementation and its behavioral description makes it hard to ensure that the synthesized implementation indeed conforms to its behavioral description. On the other hand, many employed behavioral synthesis transformations include complex optimizations to satisfy the growing demands of performance and power. Consequently, current synthesis tools are often either (a) error-prone or (b) overly conservative, thus often producing circuits of poor quality and performance. Therefore, developing tools and technologies to ensure correctness of behavioral synthesis tools is a critical issue to bring behavioral synthesis into practice. This is the main motivation of this dissertation research.

#### 1.1.2 Problem Statement

To ensure correctness of behavioral synthesis, we employ a formal verification technique called sequential equivalence checking (SEC). We need to address the following three key research challenges brought about by the semantic gap between ESL and RTL descriptions of the same hardware:

- How can we build a practical sequential equivalence checking framework? The significant semantic gap makes the direct equivalence checking between ESL and RTL impractical. The challenge is to effectively close the semantic gap and build a practical checking framework.

- How can we scale to industry designs? The scale of real-world industrial designs synthesized by a state-of-the-art behavioral synthesis tool is typically tens of thousands of lines of RTL. The running time for equivalence checking is exponential in the size of a design. Due to the semantic gap, the existing optimizations for traditional hardware verification cannot be directly applied. To make our approach scalable, we need to develop optimizations that specially target equivalence checking for behavioral synthesis.

• How can we verify the correctness of overlapping executions introduced by pipelines? Loop pipelining and function pipelining are key transformations to improve the quality of results (QoR) of RTL implementations generated by behavioral synthesis. Loop pipelining reduces the latency of synthesized designs by concurrently executing operations in successive loop iterations. Function pipelining improves the throughput by allowing operations from successive invocations of a function to execute in parallel. However, they are complex transformations involving aggressive scheduling strategies to allow overlapping executions and careful control generation to eliminate hazards. This makes formal equivalence checking even more challenging.

## 1.2 CONTRIBUTION

We developed a scalable SEC framework for certifying behavioral synthesis flows, that makes use of the intermediate design representation from the synthesis tool as well as other synthesis information to achieve scalability. We defined a graph-based representation of the ESL specification, namely Clocked Control/Data Flow Graph (CCDFG) as the intermediate design representation. In particular, this dissertation makes the following contributions:

- A scalable SEC algorithm based on symbolic simulation for comparing CCD-FG and RTL. Equivalence checking involves a word-level dual-rail symbolic simulation, which simulates two design representations simultaneously. In our approach, we simulate the CCDFG and the RTL implementation, respectively, and their simulations are synchronized by clock cycle.

- A set of key optimizations, which exploit the close correspondence between CCDFGs and their synthesized RTL designs. *Cutpoints* reduce lengths of symbolic expressions by replacing verified sub-circuits by new symbol values.

Cut-loop partitions SEC for a loop into three checks to avoid expensive fixpoint computation. Modular analysis optimizes SEC by replacing verified sub-modules by uninterpreted functions.

- An approach to certifying behaviorally synthesized loop pipelines. Our approach works by (1) constructing a provably correct loop pipeline reference model from the ESL specification, and (2) applying sequential equivalence checking between this reference model and synthesized RTL. The key insight is that a parameterized, synthesis-guided reference transformation on CCDFG permits comparison with RTL even after mappings with the original ESL specification have been destroyed by an aggressive transformation such as pipelining. Furthermore, the approach permits smooth integration with pipeline-oblivious optimizations such as cut-loop.

- An approach to certifying function pipelining in behavioral synthesis. We develop a reference function pipelining transformation, which takes certain pipeline parameters from behavioral synthesis to generate a pipeline reference model. The key is that bubble insertion is faithfully captured by symbolically encoding bubbles in the reference model. We check the equivalence between the reference model and the RTL implementation. The mapping between behavioral level operations and RTL functional units are still preserved, therefore some key optimizations, such as cutpoints, are applicable.

Note that certification with our approach assumes that the high-level transformations performed by behavioral synthesis before pipelining are correct. Such transformations are typically compiler transformations (e.g., loop unrolling, code motion, dead code elimination, etc.) and scheduling. Certainly many of these transformations are complex, and a complete certification of the synthesis flow requires certification of these high-level transformations as well. We do not address

certification these high-level transformations for this dissertation for several reasons. First, these transformations are generic compiler transformations. For instance, AutoESL, a widely used commercial synthesis tool, and LegUp, an academic synthesis tool, make use of the open-source LLVM compiler transformations [50]. As such they are more trusted than the low-level transformations which often involve manual tweaks to squeeze out extra efficiency. Second, these transformations are already being studied elsewhere in the context of compiler verification [48, 67, 74]. Finally, related efforts at the University of Texas and the Portland State University are focused on the use of theorem proving techniques for certification of many of the high-level transformations necessary. When combined with their certified transformations, our framework can be used to certify an entire synthesis flow.

#### 1.3 RELATED WORK

Several early approaches have been proposed to verify the correctness of the pioneering behavioral synthesis tools. An early effort on verification of high-level synthesis targeting the behavioral portion of VHDL was proposed by Chapman [14], which aimed to verify parts of a high-level synthesis system by giving semantics to the representation languages used. A translation from behavioral VHDL to dependence flow graphs [36] was verified by structural induction based on the CSP [32] semantics. There has been research on certified synthesis of hardware from formal languages such as HOL [28] in which a compiler that automatically translates recursive function definitions in HOL to clocked synchronous hardware has been developed. A certified hardware synthesis from programs in Esterel (a synchronous design language) has also been developed [61] in which a variant of Esterel was embedded in HOL to enable formal reasoning.

There has been much research on sequential equivalence checking between RTL and gate-level hardware designs [4, 38]. Research has also been done on combinational equivalence checking between high-level designs in software-like languages

(e.g., SystemC) and RTL designs [33]. There has also been effort for SEC between software specifications and hardware implementations [21]: GSTE assertion graphs [73] were extended so that an assertion graph edge have pre and post condition labels, and also associated assignments that update state variables. There has also been work on equivalence checking with other graph representations, e.g., Signal Flow Graph [17].

In recent years, promising progress on equivalence verification between systemlevel models and RTL has been made in both academia and industry [53]. Kundu et al. [46] presents an approach to validate the result of behavioral synthesis using insights from translation validation, automated theorem proving and relational approaches to reasoning about programs. This approach targeted compiler transformations, so it cannot verify the correctness of scheduling, binding and finite state machine (FSM) generation. Clark et al. [18] proposed an algorithm that checks behavioral consistency between an ANSI-C program and a circuit given in Verilog using Bounded Model Checking. Both the circuit and the program are unwound and translated into a formula that represents behavioral consistency. The formula is then checked using a SAT solver. Kroening [44] has further enhanced this algorithm by using predicate abstraction and induction. These approaches aim to check if the RTL holds the same property as the corresponding ANSI-C program, not equivalence checking. The Sequential Logic Equivalence Checker (SLEC) from Calypto [12] can verify RTL implementations using system models written in C/C++ or SystemC, without requiring additional testbenches or assertions. SLEC utilizes a novel technique to reduce the SEC problem to a cycleaccurate designs from the original designs, on which standard equivalence checking techniques can then be deployed [15]. Hector [42] from Synopsys is a formal equivalence checking framework to address the system level to RTL formal verification problem, which integrates multiple bit-level and word-level equivalence checking techniques. It employs an efficient formal model constructed from high-level descriptions using symbolic simulation [43]. Several optimizations can be applied to minimize the size of the formal model to reduce the complexity. Furthermore, an approach has been proposed to handle memory interfaces by using memory mapping provided by the user as invariants for an induction proof [41]. However, these two industrial tools do not have published benchmarks for comparison.

There is a significant literature on verifying pipelined microprocessors [10, 37, 49, 69], which has parallels with our work. Comparing function pipelines generated by behavioral synthesis with pipelines in microprocessors, certifying pipelines generated by behavioral synthesis is more challenging due to: (1) pipelines can be very deep; (2) each pipeline stage can be quite complex. There has been very little published work on formal verification of pipelines generated by behavioral synthesis. Nevertheless, any viable SEC framework for behavioral synthesis must handle pipelining transformations. To our knowledge current implementations either involve cost-prohibitive input-output comparison or require the user to provide the requisite mappings.

#### 1.4 DISSERTATION OUTLINE

The rest of this dissertation is organized as follows. In Chapter 2, we give a brief overview of background including behavioral synthesis flows and verification technologies. In Chapter 3, we present our intermediate representation and discuss in detail our approach to equivalence checking based on word-level symbolic simulation. In Chapter 4, we discuss three optimizations targeting different design features. We illustrate our approach to equivalence checking for behaviorally synthesized loop pipelines and function pipelines in Chapter 5 and Chapter 6, respectively. In Chapter 7, we summarize the contribution and discuss future work.

#### Chapter 2

#### **BACKGROUND**

#### 2.1 BEHAVIORAL SYNTHESIS

With the rapid increase of complexity in System-on-Chip (SoC) designs, the Electronic Design Automation (EDA) community is becoming more interested in designing hardware with a behavioral level model, rather than an RTL description. This and the increased use of high-level languages in behavioral modeling has led to a renewed interest in behavioral synthesis, both in industry and in academia [70].

A behavioral synthesis tool accepts a behavioral description, together with a library of hardware resources; it performs a sequence of transformations on the description to generate an RTL implementation. The transformations can be roughly partitioned into the following three phases.

- The first phase involves *compiler transformations*. These include loop unrolling, common subexpression elimination, etc. Furthermore, expensive operations (e.g., division) are often replaced with simpler ones (e.g., subtraction).

- The second phase is scheduling, which determines the clock step for each operation. The ordering between operations is constrained by the data and control dependencies. Scheduling transformations include chaining operations across conditional blocks and decomposing one operation into a sequence of multi-cycle operations based on resource constraints.

• The third phase is resource binding and control synthesis, which binds operations to functional units, allocates and binds registers, and generates the control circuit to implement the schedule.

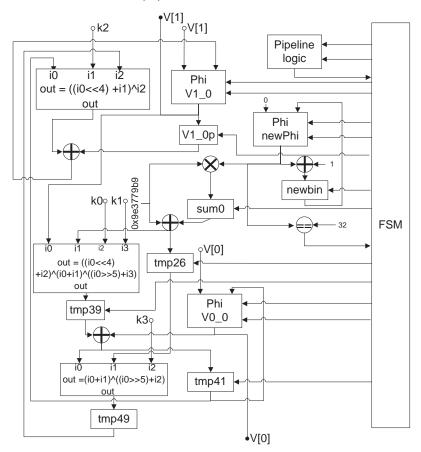

After these transformations, the RTL implementation is generated, which is subjected to further manual optimizations to fine-tune for performance and power. Each synthesis transformation is non-trivial. The result of their composition is a hardware implementation with large semantic distance from its input description. As an example, consider the synthesis of the Tiny Encryption Algorithm (TEA) [71]. Figure 2.1 shows a high-level C specification and the circuit synthesized by AutoESL. TEA, of course, is only a pedagogical algorithm, and indeed, rather weak in cryptographic strength; nevertheless, the example highlights some transformations involved in behavioral synthesis. The following transformations are involved in synthesis of the circuit.

- In the first phase, *constant propagation* removes unnecessary variables and operations.<sup>1</sup> For instance, variable *delta* is replaced by constant value.

- In the second phase, a key scheduling transformation performed is *pipelining*, to enable overlapping execution of operations from different loop iterations.

- In the third phase, operations are bound to hardware resources (e.g., the "+" operation to a hardware adder); furthermore, a finite-state machine is generated to control circuit operations.

Each synthesis transformation must respect a number of implicit design invariants. For instance, paralleling operations along different loop iterations must avoid race conditions, and scheduling must respect underlying data dependencies. Since such considerations are entangled with low-level optimization heuristics, it is easy

$<sup>^{1}</sup>$ Another compiler transformation that could be performed is loop unrolling. We avoided it for presentation simplicity.

```

void encrypt (uint32_t* v, uint32_t* k) {

uint32_t v0=v[0], v1=v[1], sum=0, i;

uint32_t delta=0x9e3779b9;

uint32_t k0=k[0], k1=k[1], k2=k[2], k3=k[3];

for (i = 0; i < 32; i++) {

sum += delta;

v0 += ((v1 << 4)+ k0) ^ (v1 + sum) ^ ((v1 >> 5) + k1);

v1 += ((v0 << 4)+ k2) ^ (v0 + sum) ^ ((v0 >> 5) + k3);

}

v[0]=v0; v[1]=v1;

}

```

# (A) C code for TEA

(B) Schema of RTL

Figure 2.1: Input and output of behavioral synthesis

to have errors in the synthesis tool itself, leading to synthesis of buggy designs. On the other hand, the semantic distance pointed to above makes direct comparison of executions of the synthesized RTL and its input description very challenging if not infeasible. Indeed, attempts to perform such comparison through sequential equivalence checking requires full, cost-prohibitive symbolic co-simulation between the C and the RTL to check their input/output correspondence [33].

#### 2.2 SOLVER TECHNOLOGY

## 2.2.1 Binary Decision Diagram

Binary Decision Diagrams (BDDs) have been widely employed in many applications. Though BDDs are not new [47], Bryant's pioneering work renewed the interest of many researchers [8]. He proposed Reduced Ordered Binary Decision Diagrams (ROBDDs, or OBDDs for short). The key insight is that reduced and ordered binary decision diagrams are a canonical representation of Boolean functions. Canonicity reduces the semantic notion of equivalence to the syntactic notion of isomorphism. Thus, checking the equivalence of two Boolean formulas can be reduced to comparisons of BDDs which can be checked in constant time.

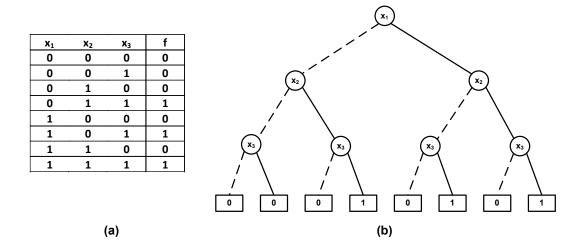

Given a Boolean function, it can be represented as a rooted, directed acyclic graph, which is actually a tree. Figure 2.2 (b) illustrates a representation of function  $f(x_1, x_2, x_3)$  defined by the truth table given in Figure 2.2 (a). The variable ordering is given as  $x_1 < x_2 < x_3$ . Each nonterminal vertex v has arcs directed toward two children: lo(v) (shown as a dashed line) corresponding to the case where v is assigned 0, and hi(v) (shown as a solid line) corresponding to the case where v is assigned 1. Each terminal vertex is labeled 0 or 1. For a given assignment to the input variables of f, the return value of f can be determined by a path from the root to a terminal vertex, following the branches indicated by the values of nonterminal vertices.

Figure 2.2: Decision tree representation

A decision tree can be reduced to a BDD by applying the following three transformations: (1) Remove duplicate terminals. This transformation eliminates all but one terminal vertex with a given label and redirects all arcs into the eliminated vertices to the remaining one (shown in Figure 2.3 (a)). (2) Remove duplicate nonterminals. In this step, if nonterminal vertices u and v have lo(u) = lo(v), and hi(u) = hi(v), then one of the two vertices can be eliminated. All incoming arcs to the eliminated one are redirected to the other vertex (shown in Figure 2.3 (b)). (3) Remove redundant tests. If nonterminal vertex v has lo(v) = hi(v), then this vertex can be eliminated. All incoming arcs to v are redirected to one of its children (shown in Figure 2.3 (c)).

BDDs have proven to be a successful representation for model checking on many practical applications. However one limitation of BDD-based approaches is that the size of the BDD heavily depends on the variable ordering. For instance, given a Boolean expression  $a_1 \cdot b_1 + a_2 \cdot b_2 \dots + a_n \cdot b_n$ , ordering variables as  $a_1 < b_1 < \dots < a_n < b_n$  yields an BDD with 2n nonterminal vertices. On the other hand, ordering variables as  $a_1 < \dots < a_n < b_1 < \dots < b_n$  yields an BDD with  $2(2^n-1)$  nonterminal vertices. For large values of n, the exponential growth of the

Figure 2.3: BDD transformations

second ordering has a dramatic effect on runtime and memory usage comparing with the first linear growth. Unfortunately, finding the best variable ordering is an NP-complete problem. In practice, the ordering is chosen either manually or by a heuristic analysis of the particular system to be represented [24, 51, 35].

# 2.2.2 Boolean Satisfiability Problem

Boolean Satisfiability (SAT) is a decision problem of determining if there exist suitable value assignments to the variables to satisfy the propositional logic formula. SAT is the first known example of NP-complete decision problem [19], which means that, unless P = NP, all SAT algorithms require worst-case exponential time. Modern SAT algorithms are effective to deal with large search spaces by exploiting the structure of the problem [65, 55, 27]. SAT techniques are widely used in a number of areas, such as combinational equivalence checking [7], model checking [6, 63], automatic test pattern generation (ATPG) [16], FPGA routing [56] and planning [40].

Currently, most state-of-the-art SAT solvers require the propositional formulas to be represented in Conjunctive Normal Form (CNF) as defined in Definition 3 [34]. A CNF formula may be viewed as a set of clauses and a clause may be viewed as a set of literals.

**Definition 1 Literal.** A literal is either a variable p or its negation  $\neg p$ . The first case is called a positive literal; the second is called a negative literal.

**Definition 2 Clause.** A clause is a finite disjunction of literals, e.g.,  $l_1 \lor l_2 \lor l_3 \ldots$ , where  $l_i$  is a literal.

**Definition 3 Conjunctive Normal Form.** A propositional formula is in Conjunctive Normal Form (CNF) if it is a finite conjunction of clauses, e.g.,  $C_1 \wedge C_2 \wedge C_3 \dots$ , where  $C_i$  is a clause.

An assignment A for a set of variables X is a function  $A: X \to \{0, u, 1\}$ , where  $0 \le u \le 1$ . Here, 0 and 1 represent false and true, respectively. Given an assignment, clauses and CNF formulas can be characterized as unsatisfied, satisfied, or unresolved [64]. The SAT problem for a CNF formula  $\varphi$  consists in deciding whether there exists an assignment to the problem variables, such that  $\varphi$  is satisfied, or proving that no such assignment exists. An assignment that satisfies a formula  $\varphi$  is called a satisfying assignment.

A combinational circuit can be translated into some intermediate representation, which can be used to generate CNF formulas. Combinational Boolean circuits [6] is one of the most accepted intermediate representations. Combinational Boolean circuits are composed of gates and connections between gates. In Combinational Boolean circuits, the notation  $y = Op(x_1, x_2)$  denotes a gate which has two inputs  $x_1$  and  $x_2$  and single output y, and Op is one of the basic logic operations, such as AND, OR, etc. Converting Boolean circuits to CNF is straightforward, and follows the procedure first outlined by G. Tseitin [68].

## 2.2.3 Satisfiability Modulo Theories

Although SAT solvers have achieved success in many practical applications, some applications require greater modeling flexibility than plain SAT; for instance, a theory of array of integers is more effective in modeling memory usage of a program. On the other hand, general-purpose first-order theorem provers are typically not able to solve such formulas directly. The main reason for this is that many applications require not only general first-order satisfiability, but rather satisfiability with respect to some background theory, which fixes the interpretations of certain predicate and function symbols [2].

Satisfiability Modulo Theories (SMT) is the problem of deciding the satisfiability of a first-order formula with respect to some decidable first-order theory  $\mathcal{T}$ . It requires deciding the satisfiability of formulae which are Boolean combinations of atomic Boolean propositions and atomic propositions in  $\mathcal{T}$ , so that Boolean reasoning is carried out by powerful SAT solvers while reasoning in the theory  $\mathcal{T}$  is carried out by efficient theory-specific decision procedures.

Most SMT solvers use Nelson-Oppen [57] method which combines decision procedures for different decidable theories under certain conditions to generate a decision procedure for their composition. These solvers support the theories of integers, reals, lists, arrays, bit vectors, etc. Therefore, it allows us to model hardware circuits at word-level rather than bit-level. SMT solvers also support uninterpreted functions. For instance, an SMT solver can determine whether f(x) = f(y), if x = y. This allows us to model the hierarchies in hardware circuits by modeling a lower-level circuit as an uninterpreted function.

Currently there are two main approaches to SMT solving: eager and lazy [42]. Eager SMT solvers first try to solve the word-level problem by employing preprocessing, rewrites and abstraction. If the rewrites are not sufficient, the word-level formula is translated into a bit-level formula and use a SAT solver to determine the satisfiability. One of the advantages of eager SMT solvers is that they can

directly leverage any efficient SAT solver. Some eager SMT solvers are BAT [52] and STP [26]. In contrast, lazy SMT solvers integrate theory specific procedures for the background theory with a SAT-solver. A given formula  $\phi$  is abstracted to a Boolean formula  $\phi_b$ . The abstraction is generated by replacing all atomic theory predicates in  $\phi$  by Boolean variables. The Boolean variables of the abstracted formula  $\phi_b$  are sub-formulas of formula  $\phi$  corresponding to sub-formulas of the background theory. The satisfiability of  $\phi_b$  is checked using a SAT solver. If  $\phi_b$  is unsatisfiable, then  $\phi$  is also unsatisfiable. Some lazy SMT solvers are Yices [20] and CVC3 [3].

In this research, we employ CVC3, one of the most successful SMT solvers, which is being developed at New York University and University of Iowa. CVC3 provides several different user interfaces including high-level APIs for both C and C++, an interactive command-driven interface, and a file interface.

# 2.3 SCALABLE VERIFICATION TECHNIQUES

## 2.3.1 Symbolic Simulation

Simulation is the most common method for testing and debugging hardware designs. But the problem is that one simulation run can only validate one test case. To fully verify a hardware design, engineers must exhaustively simulate the entire set of test cases to explore the whole state space, which is extremely time-consuming. Symbolic simulation allows us to compute information on the entire set of values in a single simulation run, because the set of test vectors is encoded symbolically, instead of using a specific element of the set [9]. This approach dramatically improves the efficiency of design validation.

Consider a 2-bit AND operator which has two 2-bit inputs A and B and a 1-bit output C. In order to fully verify this operator, a conventional simulator must try all 16 possible test vectors. But for symbolic simulation, we treat the inputs as

two 2-bit symbols A and B and the output of the simulation is  $C = A \wedge B$  by only one simulation run.

However, symbolic simulation also has two main bottlenecks when applying to verify large designs [33]. First, because symbolic simulation enumerates all possible execution paths, the number of paths to be explored may grow exponentially. Second, the terms representing the symbolic values of variables may also blow-up exponentially. Moreover, symbolic exploration of loops may lead to long executions, which may cause further blow-up. Although modern SMT solvers are able to handle such blow-ups to a certain extent, the performance is reduced significantly [66].

## 2.3.2 Equivalence Checking for Logic Synthesis

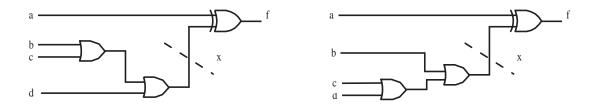

Our research leverages the success of equivalence checking for logic synthesis [33, 5, 7], and employs these ideas for equivalence checking for behavioral synthesis. Next, we provide an overview of the equivalence checking concepts.

Equivalence checking between RTL descriptions and gate-level implementations of combinational circuits is a mature field with decades of research [38, 4]. To check whether two combinational circuits are functionally equivalent, we need to prove that, for all possible inputs, both combinational circuits have the same outputs. Hardware circuits are modeled as Boolean expressions, so the problem of checking whether two circuits are equivalent is converted to the problem of determining whether two Boolean expressions are equivalent.

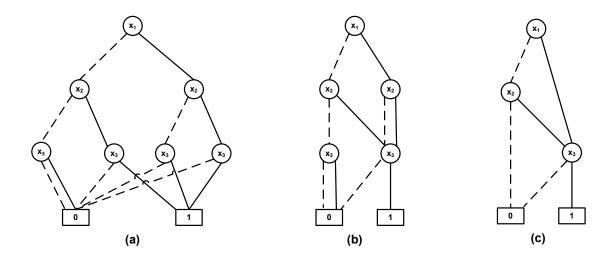

Consider the simple example in Figure 2.4. We can use symbolic simulation to compute the relationship between inputs and outputs. Given the two circuits and the same input symbols, the outputs are symbolic expressions in terms of the inputs. For the left-hand circuit in Figure 2.4, the value of the final output f is  $a \oplus (b \wedge c) \wedge d$ . Similarly, we can compute that the output of the right-hand circuit is  $a \oplus (b \wedge (c \wedge d))$ . To verify the equivalence of these two circuits, we just

Figure 2.4: Simple cut-point example

need to verify whether these two expressions are equivalent.

As discussed above, one bottleneck of symbolic simulation is the exponential blow-up of the expression lengths. The major practical reduction technique for combinational equivalence checking is cut-points [5, 7]. The main idea is to look for the corresponding points in the two circuits that can be proven to be equivalent; then the equivalent circuits can be cut out of circuits and replaced by new primary symbols. For instance, in Figure 2.4, to introduce cut-point x, we first verify that  $(b \wedge c) \wedge d$  is equivalent to  $b \wedge (c \wedge d)$ . Then we cut the sub-circuits off and introduce new symbol x to represent the equivalent circuits. Then we can verify that f is equivalent to g because they are both equal to g and g are inequivalent. The reason is that when we introduce new symbols for cut-points, we may lose constraints. The situation that two circuits are equivalent but equivalence checker reports inequivalence is called false negative. In general, the solution to this problem is to re-introduce constraints on the cut-points [33, 7].

#### Chapter 3

# EQUIVALENCE CHECKING

In this charpter, we present a graph-based design representation, called Clock Control/Data Flow Graph (CCDFG), as our intermediate representation. Our equivalence checking between a CCDFG and its synthesized RTL implementation is based on dual-rail symbolic simulation. The checking approach has been implemented to be fully automatic.

## 3.1 CLOCKED CONTROL/DATA FLOW GRAPHS

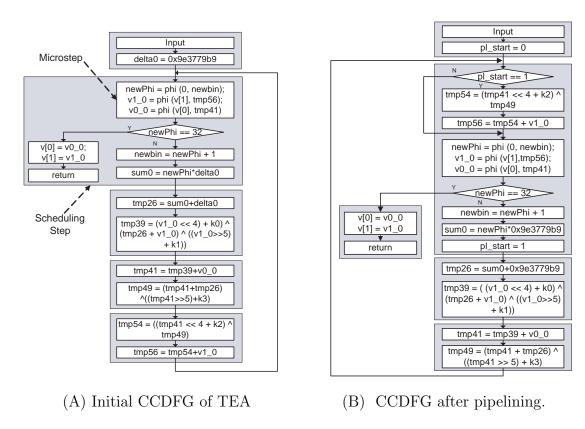

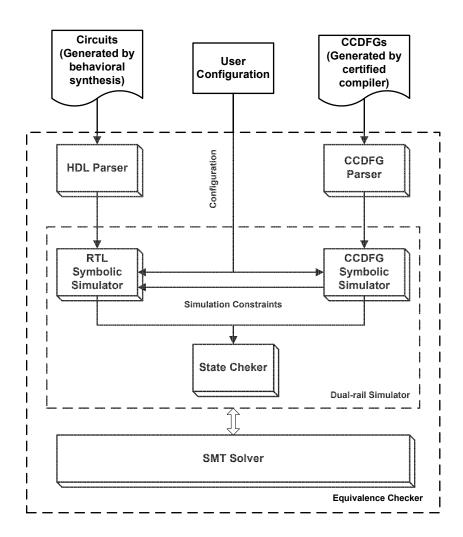

A CCDFG can be viewed as a formal control/data flow graph (CDFG) — used as internal representation in most synthesis tools — augmented with a schedule. The semantics of CCDFG are formalized in the logic of the ACL2 theorem prover [39]. Figure 3.1 shows two CCDFGs for the TEA encryption function: an initial CCDFG derived from the C code, and its successive transformation after pipelining. This section briefly discusses the formulation of a CCDFG; for a more complete account, see [59].

The formalization of CCDFG assumes that the underlying language provides the semantics for primitive operations (e.g., arithmetic operations, comparison, etc.). The key components of the formalization are (1) control and data flow graphs, (2) microstep partition, and (3) schedule. Following standard conventions, the control flow is broken up into of basic blocks; correspondingly data dependencies follow the "read after write" paradigm:  $op_j$  is dependent on  $op_i$  if  $op_j$  occurs after  $op_i$  in a control path and computes an expression over some variable v that is

Figure 3.1: CCDFGs for the TEA encryption function

assigned most recently by  $op_i$  in the path. A microstep partition is a partitioning of operations in a basic block such that if  $op_i$  and  $op_j$  are in the same partition then their execution order is irrelevant to control and data dependencies. Each component of a microstep partition is a microstep. A schedule is a grouping of microsteps; informally, if  $m_0$  and  $m_1$  belong to the same scheduling step then they are executed within the same clock cycle. A CCDFG execution is formalized through state-based semantics. A CCDFG state (resp., CCDFG input) is a valuation of the state (resp., input) variables. Given a sequence of inputs, an execution of a CCDFG G with microstep partition G and schedule G is a sequence of CCDFG states that corresponds to an evaluation of the microsteps of G respecting G.

Remark Conventions. For a given CCDFG  $G \triangleq \langle G_{CD}, M, T \rangle$  and a set  $t \in T$ , we

use the term "projection of G on t" to mean the CCDFG  $G_t \triangleq \langle G'_{CD}, M', \{t\} \rangle$  where  $G'_{CD}$  and M' contain only the operations in  $G_{CD}$  and M respectively, that are members of t. For a set  $T_0 \subseteq T$ , we use "projection of G on  $T_0$ " to denote the following graph G'. The nodes of G' are given by the set  $\mathcal{N} \triangleq \{G_t : t \in T_0\}$ ; given  $g_0, g_1 \in \mathcal{N}$ , there is an edge from  $g_0$  to  $g_1$  if there are operations  $g_1$  and  $g_2$  such that  $g_1 \in g_0$ ,  $g_2 \in g_1$  and there is an edge from  $g_1$  to  $g_2$  in  $g_2$ .

Since a schedule is a partition of microsteps,  $T_0$  induces a partition of  $G_{CD}$  such that if  $t_0 \neq t_1$  the partition induced by  $t_0$  is disjoint from that induced by  $t_1$ . Given a set T of scheduling steps, one can describe the CCDFG  $G \triangleq \langle G_{CD}, M, T \rangle$  uniquely as the triple  $\langle S, E, M \rangle$  where S and E denote the nodes and edges of the projection of G on T, and M is the set of microstep partitions refined by T. We use this view in the rest of the dissertation.

## 3.2 CIRCUIT MODEL

We represent a circuit as a Mealy machine specifying the updates to the state elements (latches) in each clock cycle. Our formalization of circuits is typical in traditional hardware verification, but we make combinational nodes explicit to facilitate the correspondence with CCDFGs. A circuit is a tuple  $M = \langle I, N, F \rangle$  where I is a vector of inputs; N is a pair  $\langle N_c, N_d \rangle$  where  $N_c$  is a set of combinational nodes and  $N_d$  is a set of latches; and F is a pair  $\langle F_c, F_d \rangle$  where  $F_c$  maps each combinational node  $c \in N_c$  to an expression over  $N_c \cup N_d \cup I$  and for each latch  $d \in N_d$ ,  $F_d$  maps each latch d to  $n \in N_c \cup N_d \cup I$  where  $F_d$  is a delay function which takes the current value of n to be the next-state value of d.

A circuit state is an assignment to the latches in  $N_d$ . Given a sequence of valuations to the inputs  $i_0, i_1, \ldots$ , a circuit trace of M is the sequence of states  $s_0, s_1, \ldots$ , where (1)  $s_0$  is the initial state and (2) for each j > 0, the state  $s_j$  is obtained by updating the elements in  $N_d$  given the state valuation  $s_{j-1}$  and input valuation  $i_{j-1}$ . The

Figure 3.2: Operation mapping between CCDFG and circuit

observable behavior of the circuit is the sequence of valuations of the outputs which are a subset of latches and combinational nodes.

#### 3.3 CORRESPONDENCE BETWEEN CCDFGS AND CIRCUITS

Given a CCDFG G and a synthesized circuit M, it is tempting to define a notion of correspondence as follows: (1) establish a fixed mapping between the state variables of G and the latches in M, and (2) stipulate an execution of G to be equivalent to an execution of M if they have the same observable behavior. However, this does not work in general since the mappings between state variables and latches may be different in each clock cycle. To address this, we introduce  $EMap: ops \rightarrow N_c$ , mapping CCDFG operations to the combinational nodes in the circuit: each operation is mapped to the combinational node that implements the operation;

the mapping is independent of clock cycles. Figure 3.2 shows the mapping for the synthesized circuit of TEA. Recall from Section 2.1 that the FSM decides the control signals for the circuit; the FSM is thus excluded from the mapping.

We now define the equivalence between G and M. A CCDFG state x of G is equivalent to a circuit state s of M with respect to an input i and a microstep partition t, if for each operation op in t, the inputs to op according to x and i are equivalent to the inputs to EMap(op) according to s and EMap(i), i.e., the values of each input to op and the corresponding input to EMap(op) are equivalent, and the outputs of op are equivalent to the outputs of EMap(op).

Given a CCDFG G and a circuit M, G is equivalent to M if and only if for any execution  $[x_0, x_1, x_2, \ldots]$  of G generated by an input sequence  $[i_0, i_1, i_2, \ldots]$  and by microstep partition  $[t_0, t_1, \ldots]$  of G, and the state sequence  $[s_0, s_1, s_2, \ldots]$  of M generated by the input sequence  $[EMap(i_0), EMap(i_1), EMap(i_2), \ldots]$ ,  $x_k$  and  $s_k$  are equivalent with respect to  $t_k$  under  $i_k$ ,  $k \geq 0$ .

## 3.4 DUAL-RAIL SIMULATION FOR EQUIVALENCE CHECKING

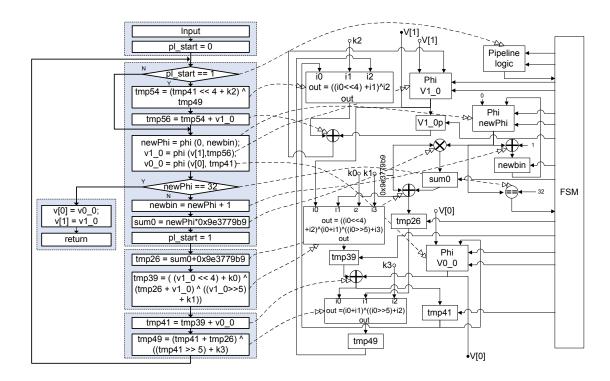

We check equivalence between CCDFG G and circuit M by dual-rail symbolic simulation (Figure 3.3); the two rails simulate G and M respectively, and are synchronized by clock cycle. The equivalence checking in clock cycle k is conducted as follows:

- 1. The current CCDFG state  $x_k$  and circuit state  $s_k$  are checked to see whether for the input  $i_k$ , the inputs to each operation op in the scheduling step  $t_k$  are equivalent to the inputs to EMap(op). If yes, continue; otherwise, report inequivalence.

- 2. G is simulated by executing  $t_k$  on  $x_k$  under  $i_k$  to compute  $x_{k+1}$  and recording the outputs of each  $op \in t_k$ . M is simulated for one clock cycle from  $s_k$  under input  $EMap(i_k)$  to compute  $s_{k+1}$ . The outputs for each op are checked for

Figure 3.3: Dual-rail simulation scheme for equivalence checking between CCDFG and circuit.

equivalence with the outputs of EMap(op). If yes, continue; otherwise, report inequivalence.

3. The next scheduling step  $t_{k+1}$  is determined from control flow. If  $t_k$  has multiple outgoing control edges, the last microstep of  $t_k$  executed is identified. The outgoing control edge from this microstep whose condition evaluates to true leads to  $t_{k+1}$ .

We permit both bounded and unbounded (fixed-point) simulations. In particular, the simulation proceeds until (i) the equivalence check fails, (ii) the end of a bounded input sequence is reached, or (iii) a fixed point is reached for an unbounded input sequence.

The bit-level and word-level checkers are complementary. The bit-level checker ensures that the equivalence checking is decidable, while the word-level checker provides the optimizations which are crucial to scalability. The word-level checker can make effective use of results from bit-level checking in many cases. One typical scenario is as follows. Suppose M is a design module of modest complexity but

is awkward to check at word-level. Then the bit-level checker is used to check the equivalence of the CCDFG of M with its circuit implementation; when the word-level checker is used for equivalence checking of a module that calls M, it skips the check of M, treating the CCDFG of M and its circuit implementation as equivalent black boxes.

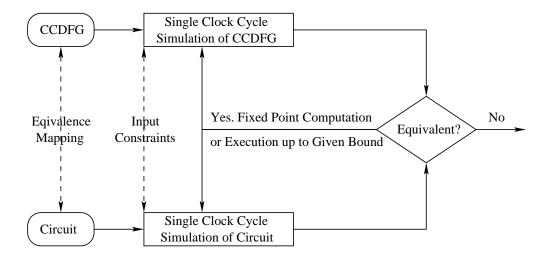

## 3.5 TOOL IMPLEMENTATION

We first implemented the dual-rail simulation on bit-level in the Intel Forte environment [62], where symbolic states are represented using BDDs. However, experimental results clearly show that bit-level checking does not scale (cf. Section 3.6). Therefore, we re-implemented our equivalence checker on word-level in OCaml [58]. This is viable since word-level mappings between operations and circuit nodes are explicit. We use bit-vectors to encode the variables in the CCDFG and the circuit; the SMT engine checks input/output equivalence and determines control paths. Our word-level checker employs CVC3 SMT engine [3]. Figure 3.4 shows the framework of our equivalence checker. Behavioral synthesis generates RTL circuits in terms of Hardware Description Languages (HDLs), such as Verilog or VHDL. Currently, we only developed the parser for Verilog, but we can easily extend our HDL parser to support VHDL. Our HDL parser parses HDL files into an intermediate representation for symbolic simulation. Our HDL parser and simulator support a synthesizable subset of HDL. This subset of HDL can be synthesized into gate-level. The CCDFG parser parses CCDFG files generated by our certified compiler. The RTL and CCDFG symbolic simulators simulate circuits and CCDFGs simultaneously, synchronized by clock cycle following our dual-rail simulation scheme. The state checker check the equivalence of the outputs of symbolic simulators by utilizing SMT solvers.

Our checker provides three optimizations targeting different circuit features (see Chapter 4). Users can specify which optimizations are involved in a particular

Figure 3.4: Framework of equivalence checker

Table 3.1: Bit-level equivalence checking statistics

| Bit Width | # of Circuit Nodes | Time (Sec.) | BDD Nodes |

|-----------|--------------------|-------------|-----------|

| 2         | 96                 | 0.02        | 503       |

| 3         | 164                | 0.05        | 4772      |

| 4         | 246                | 0.11        | 42831     |

| 5         | 342                | 0.59        | 16244     |

| 6         | 452                | 12.50       | 39968     |

| 7         | 576                | 369.31      | 220891    |

| 8         | 714                | 6850.56     | 1197604   |

check. The dual-rail simulator will be automatically configured according to the user's specification.

### 3.6 EXPERIMENTAL RESULTS

To establish a baseline, we use the bit-level checker on a set of CCDFGs for GCD and the corresponding circuits synthesized by AutoESL. The experiments were conducted on a workstation with 3GHz Intel Xeon processor with 2GB memory. The checking time bound is set up to 4 hours.

Table 3.1 shows the results of bit-level SEC for GCD. GCD contains a loop whose number of iterations depends on the inputs. Since all operations are decomposed into bit-level, the running time grows exponentially with bitwidth. For 8-bit GCD, SEC takes about 2 hours. Pure bit-level SEC is thus not feasible for more complex designs.

To experiment with our word-level checking scheme, we have checked several designs which have different design features. The statistics are shown in Table 3.2. "-" signifies "out of time or memory". DCT (Discrete Cosine Transform) is a widely used algorithm in image processing domain, which contains sequential computation

Table 3.2: Word-level equivalence checking statistics

| Design                   | GCD | TEA  | DCT  | 3DES  |

|--------------------------|-----|------|------|-------|

| C Code Size (# of Lines) | 14  | 12   | 52   | 325   |

| RTL Size (# of Lines)    | 364 | 1001 | 688  | 18053 |

| Time (Seconds)           | -   | -    | 30.1 | -     |

| Memory (Megabytes)       | -   | -    | 49.2 | -     |

without loop. SEC for DCT only takes half a minute. Unfortunately, we cannot finish the checking for GCD, TEA, and 3DES. These designs either requires a very expensive fix-point computation or have complex modular hierarchies. Next, we present how to further optimize our checking scheme in Chapter 4.

## Chapter 4

### **OPTIMIZATIONS**

### 4.1 MOTIVATION AND OVERVIEW

In Chapter 3, we proposed a framework for certifying behaviorally synthesized RTL through SEC with our CCDFG representation. However, we realized that naive word-level checking ran into scalability issues. In this chapter, we present a suite of optimizations for the SEC step above, which exploit both the explicit control and data flow representations in the CCDFG and the module structures in the ESL description. We have applied these optimizations in verification of RTL synthesized by AutoESL Our experiments show that they scale SEC to tens of thousands of lines of synthesized RTL from complex behavioral specifications (e.g., unbounded loops, modules, etc.), making it viable for industrial designs. We know of no other SEC framework that can handle behaviorally synthesized RTL of such complexity.

### 4.2 CUT-POINTS

The cutpoint optimization involves pre-verifying comparison of specific CCDFG operations and their circuit implementations off-line. Subsequently, during SEC, these operations are replaced in the CCDFG and RTL by equivalent symbols. Note that only the equivalences (not computations) are relevant to SEC; if the inputs to a cutpoint are equivalent, their outputs can be replaced by equivalent symbols, causing only equivalences (not outputs themselves) to be propagated.

We utilize two types of cutpoints, combinational and sequential. Combinational cutpoints are applicable to combinational portions, and have been studied extensively [45]. RTL designs with complex combinational circuits are generated due to transformations such as loop unrolling: in the TEA example, the behavioral synthesis tool can fully unroll the for loop, creating complex combinational circuits by aggregating operations from different iterations. Sequential cutpoints cut sequential circuits and keep complex expressions from propagating across clock cycles.

In the TEA example (Figure 3.2), the scheduling step starting with the conditional  $pl\_start=1$  and ending with the assignment  $pl\_start=1$  is implemented as a combinational block that can be cut at all operations, e.g., the one computing tmp54; the equivalence of this operation with the corresponding RTL is certified separately (e.g., by theorem proving). On the other hand, the operation that computes tmp49 can be used as a sequential cutpoint since it connects two scheduling steps.

To explain the role of post-scheduling CCDFGs in cutpoint optimization, note that the ESL specification is unclocked while the RTL is clocked. Furthermore, after application of high-level transformations, the RTL has little correspondence in internal operations with the behavioral description, making it difficult to identify cutpoints. However, this problem is eliminated in our framework since there is a readily available correspondence with the post-scheduling CCDFG, e.g., the operation-to-resource mapping, which provides natural candidates for cutpoints.

## 4.3 CUT-LOOP OPTIMIZATION

A major challenge in SEC is termination, which typically requires expensive fixed-point computation. Termination becomes a problem when the input description contains unbounded loops. Consider the CCDFG of the Greatest Common Divisor (GCD) algorithm shown in Figure 4.1. The bit-level symbolic simulation for GCD,

```

a=A

b=B

int gcd (int a, int b)

Micro Step-

{

a >= b

int t;

True

do {

False

a=a-b

if (a >= b) a=a-b;

True

else { t=a ; a=b ; b=t ; }

t=a;a=b;b=t

while (b != 0);

b!=0

return a;

Scheduling

False

Step

}

return a

```

Figure 4.1: C source code and CCDFG for GCD

even for 8-bit integers, involves more than 6850 seconds and 1197606 BDD nodes (cf. Section 3.6). A naive fixed-point computation at word-level is also expensive. Even for designs with deep bounded loops (e.g., TEA), full unrolling is too expensive for both bit-level and word-level simulations.

Our solution is the *cut-loop optimization*, which "cuts" the loop, reducing the fixed-point computation to three checks, *i.e.*, at the entry, body, and exit. The idea is inspired by theorem proving approaches to verifying software loops. At entry, we check equivalence between the CCDFG and the RTL for the path to the initial loop entry. For the body, we check that if (1) equivalence is maintained at the loop join point, and (2) the loop does not exit, then equivalence is maintained after one iteration. For the exit, we check that if (1) equivalence is maintained at the loop join point, and (2) the loop exits, then equivalence is maintained at the loop exit. The loop structure and entry point information are available from the synthesis tool. The checks above are inspired by inductive assertions in software verification [22, 31]: the three checks are essentially the proof obligations

Figure 4.2: Cut-loop optimization for GCD example

discharged by a verification condition generator, if we think of equivalence with RTL as the invariant maintained by the loop. Using ACL2, we proved that the checks guarantee word-level equivalence over the entire loop execution. The proof follows a reasoning analogous to that used in justifying the use of loop invariants to cut loops for program verification using inductive assertions.

We illustrate cut-loop optimization on the GCD example in Figure 4.2. At the loop entry, the check that a and b are equivalent to their RTL counterparts is trivially true since they are inputs. For the body check the condition  $b \neq 0$  is applied to ensure the iteration does not exit, and for the exit check the condition b = 0 is applied to ensure the loop exits. For both body and exit checks, the condition being checked is that if a and b are equivalent before executing  $a \geq b$  then they are equivalent after one iteration. With this optimization, word-level SEC on GCD finishes within two seconds. The cut-loop optimization is also useful

Figure 4.3: Modular SEC for 3DES

for deep bounded loops, e.g., we achieved major speed-up for word-level SEC on TEA (cf. Section 4.5).

Note that loop detection is greatly simplified since CCDFGs are derived from ESL designs by applying primitive transformations.

### 4.4 MODULAR ANALYSIS

Synthesized RTL is often large and complex, e.g., for 3DES design, the behavioral synthesis tool generates 18053 lines of Verilog. Behavioral synthesis reduces RTL size via modular reuse: without modules, the RTL for 3DES would be 128K lines. Modules may be present in input description or introduced by behavioral synthesis. To support modules, CCDFGs are extended with function calls. An example function invocation in the 3DES CCDFG is shown in Figure 4.3.

With modules, a given behavioral description corresponds to several CCDFGs

(each corresponding to a module). A module can be either combinational or sequential. A combinational module returns in the same clock cycle in which it is invoked, while a sequential module takes several cycles. Note that the top-level CCDFG may not capture all the scheduling steps since some are in other sequential modules. In the synthesized RTL, there is a module for each CCDFG. In addition to RTL code implementing functionality, there is additional code for interfaces, e.g., a module commonly needs reset, start, and allow signals besides input/output data signals.

One naive approach to handle modules is to unfold them, causing each module to be analyzed at each invocation. We prefer compositional analysis of each module separately. Our scheme works as follows.

- For each module M, the CCDFG and RTL for M are checked for equivalence separately.

- When verifying a module M' that invokes M, the invocation of M in the CCDFG and RTL of M' are replaced by equivalent uninterpreted functions.

The equivalence between function invocation in CCDFG and module interfacing mechanism in RTL is pre-certified. Modular analysis is possible because of explicit correspondence between the CCDFG and the RTL of a module: since we use the same module structure used in the synthesis, the decomposition does not introduce over-approximations.

Currently, we do not handle recursive modules since recursions in ESL descriptions are typically removed by compiler transformations; however, modular analysis can be extended to recursion by replacing the callee with a "module summary", analogous to procedure summaries in software verification [1].

Table 4.1: Designs, features, and optimizations

| Designs  | Features                      | Optimizations    |

|----------|-------------------------------|------------------|

| GCD      | Unbounded Loop                | Cut-Loop         |

| DCT      | Sequential without Loop       | Cutpoint         |

| TEA      | Bounded Loop                  | Cut-Loop         |

|          | Unrolled Loop                 | Cutpoint         |

| DES      | Bounded Loop                  | Cut-Loop         |

|          | Unrolled Loop                 | Cutpoint         |

|          | High Sequential Complexity    |                  |

| 3DES     | Bounded Loop                  | Cut-Loop         |

|          | Unrolled Loop                 | Cutpoint         |

|          | High Sequential Complexity    | Modular Analysis |

| 3DES_key | Bounded Loop                  | Cut-Loop         |

|          | Unrolled Loop                 | Cutpoint         |

|          | High Sequential Complexity    | Modular Analysis |

|          | High Combinational Complexity |                  |

### 4.5 EXPERIMENTAL RESULTS