## **Portland State University**

## **PDXScholar**

Dissertations and Theses

**Dissertations and Theses**

Fall 12-22-2015

# Formal Modeling and Verification of Delay-Insensitive Circuits

Hoon Park

Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Digital Circuits Commons, and the Electrical and Computer Engineering Commons

Let us know how access to this document benefits you.

#### **Recommended Citation**

Park, Hoon, "Formal Modeling and Verification of Delay-Insensitive Circuits" (2015). *Dissertations and Theses*. Paper 2639.

https://doi.org/10.15760/etd.2635

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

by

Hoon Park

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

Dissertation Committee:

Xiaoyu Song, Chair

Douglas V. Hall

Fu Li

Christof Teuscher

Jingke Li

Marly Roncken (non-voting member)

Portland State University 2015

#### Abstract

Einstein's relativity theory tells us that the notion of simultaneity can only be approximated for events distributed over space. As a result, the use of asynchronous techniques is unavoidable in systems larger than a certain physical size. Traditional design techniques that use global clocks face this barrier of scale already within the space of a modern microprocessor chip. The most common response by the chip industry for overcoming this barrier is to use Globally Asynchronous Locally Synchronous (GALS) design techniques. The circuits investigated in this thesis can be viewed as examples of GALS design. To make such designs trustworthy it is necessary to model formally the relative signal delays and timing requirements that make these designs work correctly. With trustworthy asynchrony one can build reliable, large, and scalable systems, and exploit the lower power and higher speed features of asynchrony.

This research presents ARCtimer, a framework for modeling, generating, verifying, and enforcing timing constraints for individual self-timed handshake components that use bounded-bundled-data handshake protocols. The constraints guarantee that the component's gate-level circuit implementation obeys the component's handshake protocol specification. Because the handshake protocols are delay insensitive, self-timed systems built using ARCtimer-verified components can be made delay insensitive. Any delay sensitivity inside a component is detected and repaired by ARCtimer. In short: by carefully considering time locally, we can ignore time globally.

ARCtimer applies early in the design process as part of building a library of verified components for later system use. The library also stores static timing analysis (STA) code to validate and enforce the component's constraints in any

self-timed system built using the library. The library descriptions of a handshake component's circuit, protocol, timing constraints, and STA code are robust to circuit modifications applied later in the design process by technology mapping or layout tools.

New contributions of ARCtimer include:

- 1. Upfront modeling on a component by component basis to reduce the validation effort required to

- (a) reimplement components in different technologies,

- (b) assemble components into systems, and

- (c) guarantee system-level timing closure.

- 2. Modeling of bounded-bundled-data timing constraints that permit the control signals to lead or lag behind data signals to optimize system timing.

## Dedication

This dissertation is dedicated to my wife Haera, for all her love and support.

## Acknowledgments

First of all I thank my mentor, Marly Roncken. She is enthusiastic, full of ideas, and thorough with all the details. I appreciate all her contributions in time, ideas, and funding to make my Ph.D. experience productive and stimulating. The joy and enthusiasm she has for research was contagious and motivational for me, even during tough times in the Ph.D. pursuit.

I thank my advisor, Prof. Xiaoyu Song, for his guidance, encouragement, and excellent scientific advice throughout the course of this research.

Special thanks go to Willem Mallon who built the ARCwelder compiler during the two years he joined the ARC at Portland State University. He introduced me to the theory of Delay-Insensitive algebra and developed the notion of Bounded Bundled Data (BBD), which I have formalized in this thesis.

I thank Anping He, our ARC collaborator in China, with whom we have weekly meetings. He was very instrumental in building a foundation for automating ARCtimer.

I would also like to thank my fellow ARCwelders: Ivan Sutherland for stimulating ideas and discussions, and Swetha Mettala Gilla, Chris Cowan, and Navaneeth Jamadagni, for daily companionship and laughter.

Most of all, I thank my beloved wife, Haera Chung, for her love, constant support, her prayers, and giving birth to our son, Daniel. Daniel is now five months old at 18 pounds – he is a bundle of joy.

Last but not least, I would like to thank my parents, Woe-Chul Park and Kum-ju Kim for their unending love and support. It's been a long journey.

## **Table of Contents**

| $\mathbf{A}$ | bstra | nct                                               | i    |

|--------------|-------|---------------------------------------------------|------|

| D            | edica | ation                                             | iii  |

| $\mathbf{A}$ | ckno  | wledgments                                        | iv   |

| Li           | st of | Figures                                           | viii |

| 1            | Inti  | roduction                                         | 1    |

|              | 1.1   | Motivation                                        | . 1  |

|              | 1.2   | Problem Definition                                | 5    |

|              | 1.3   | Proposed Approach                                 | . 7  |

|              | 1.4   | Contributions                                     | . 8  |

|              | 1.5   | Organization of the Dissertation                  | 11   |

| 2            | Rel   | ated Work                                         | 12   |

| 3            | Fun   | ndamentals and Semi-modularity Revisited          | 16   |

|              | 3.1   | Asynchronous Communication Channels               | 16   |

|              | 3.2   | Circuit Class                                     | 18   |

|              | 3.3   | Graphical Representation of Asynchronous Circuits | 19   |

|              | 3.4   | Gate and Wire Model                               | 21   |

|              | 3.5   | Environment Model                                 | 25   |

|              | 3.6   | Relative Timing Methodology                       | 27   |

|              | 3.7   | Semimodularity in the context of Relative Timing  | 29   |

|                                   |                                 | 3.7.1                    | Semimodularity—old definition                                     | 30  |

|-----------------------------------|---------------------------------|--------------------------|-------------------------------------------------------------------|-----|

|                                   |                                 | 3.7.2                    | Semimodularity—new definition                                     | 31  |

| 3.8 Example - C element           |                                 |                          | ple - C element                                                   | 33  |

|                                   |                                 | 3.8.1                    | Specification                                                     | 33  |

|                                   |                                 | 3.8.2                    | Implementation                                                    | 34  |

|                                   |                                 | 3.8.3                    | Applying RT constraints and enhanced semimodularity $\ . \ . \ .$ | 37  |

| 4                                 | Mo                              | deling                   |                                                                   | 41  |

|                                   | 4.1                             | Model                    | ing the Implementation                                            | 42  |

|                                   |                                 | 4.1.1                    | Circuit                                                           | 43  |

|                                   |                                 | 4.1.2                    | Environment                                                       | 45  |

|                                   |                                 | 4.1.3                    | Modeling RT constraints                                           | 48  |

|                                   | 4.2                             | Check                    | ing Specification using Properties                                | 51  |

|                                   | 4.3                             | Using                    | XDI Specifications as Monitor and Properties                      | 54  |

| 5 ARCtimer                        |                                 |                          | r                                                                 | 57  |

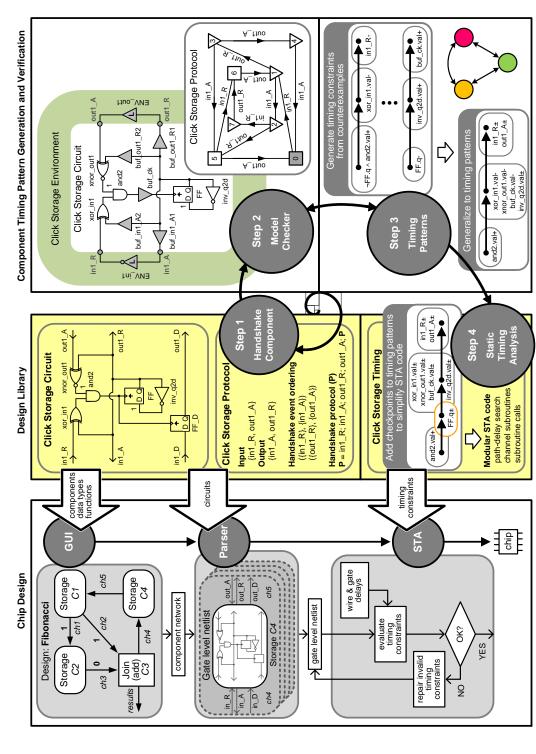

|                                   | 5.1 Timing Verification Context |                          |                                                                   | 59  |

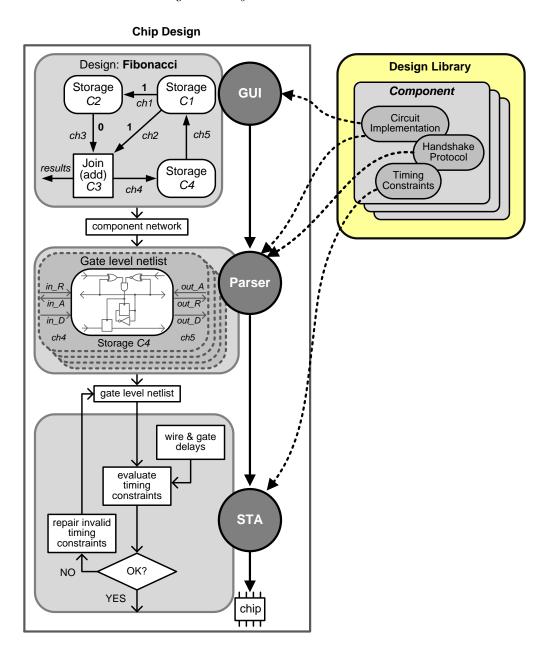

|                                   |                                 | 5.1.1                    | Design Library                                                    | 61  |

|                                   |                                 | 5.1.2                    | GUI                                                               | 61  |

|                                   |                                 | 5.1.3                    | Parser                                                            | 63  |

|                                   |                                 | 5.1.4                    | STA                                                               | 64  |

| 5.2 Timing Verification Framework |                                 | g Verification Framework | 69                                                                |     |

|                                   |                                 | 5.2.1                    | ARC<br>timer Step 1 — Handshake Component                         | 71  |

|                                   |                                 | 5.2.2                    | ARCtimer Step 2 — Model Checker                                   | 77  |

|                                   |                                 | 5.2.3                    | ARC<br>timer Step 3 — Timing Patterns                             | 91  |

|                                   |                                 | 5.2.4                    | Step 2 Revisited — Adding Timing Constraints                      | 108 |

|   |        | 5.2.5   | ARCtimer Step 4 — Static Timing Analysis            | . 112 |

|---|--------|---------|-----------------------------------------------------|-------|

|   |        | 5.2.6   | Summary Timing Verification Framework Steps 1–4     | . 118 |

| 6 | RT     | chara   | cterization of Bounded Bundled Data                 | 120   |

|   | 6.1    | Bound   | ded Bundled Data and Click Storage                  | . 120 |

|   | 6.2    | Mode    | ling Data                                           | . 122 |

|   | 6.3    | RT C    | onstraints for BBD                                  | . 124 |

|   | 6.4    | Code    | Changes and Additions in NuSMV                      | . 126 |

|   | 6.5    | Count   | ter Examples without BBD Constraints                | . 133 |

|   | 6.6    | Non-S   | Storage Component                                   | . 135 |

|   | 6.7    | STA     | Translation                                         | . 137 |

| 7 | Coı    | nclusio | on .                                                | 139   |

| R | lefere | ences   |                                                     | 142   |

| A | ppen   | ndix A  | Click Family - Protocols, Circuits, Timing Patterns | 151   |

| A | ppen   | ıdix B  | Click Verification - Time and Space Complexity      | 160   |

| A | ppen   | ndix C  | NuSMV Library Code for Click                        | 164   |

| A | ppen   | ıdix D  | NuSMV Code for Click Storage Component              | 171   |

## List of Figures

| 1.1  | An example of a glitch                                   | 6  |

|------|----------------------------------------------------------|----|

| 2.1  | RT constraint expression                                 | 12 |

| 2.2  | Simplification in synthesis                              | 13 |

| 2.3  | Constructing a process representation using DI algebra   | 14 |

| 3.1  | Timing diagram of bundled data                           | 17 |

| 3.2  | Circuit classification                                   | 19 |

| 3.3  | Example of two inverters and its state graph             | 21 |

| 3.4  | Logic gate                                               | 21 |

| 3.5  | Stable and unstable gates                                | 22 |

| 3.6  | Unstable gate becoming stable                            | 23 |

| 3.7  | Inertial delay NAND gate                                 | 23 |

| 3.8  | Semimodular NAND gate                                    | 24 |

| 3.9  | Modeling wire delays on a fork                           | 25 |

| 3.10 | Environment and circuit in relation to the specification | 26 |

| 3.11 | Example of RT over two paths and STG                     | 28 |

| 3.12 | Blocked by RT stripe convention                          | 29 |

| 3.13 | Examples of transitions under old semimodularity         | 31 |

| 3.14 | Examples of transitions under enhanced semimodularity    | 32 |

| 3.15 | C element example $\dots$                                | 33 |

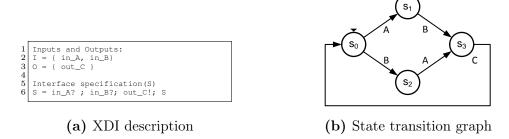

| 3.16 | XDI description of C element                             | 34 |

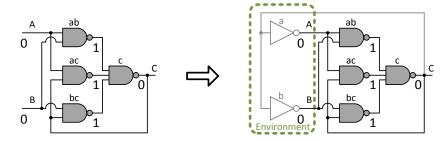

| 3.17 | SI C element NAND implementation                         | 35 |

| 3.18 | STG of C element in NAND implementation                  | 36 |

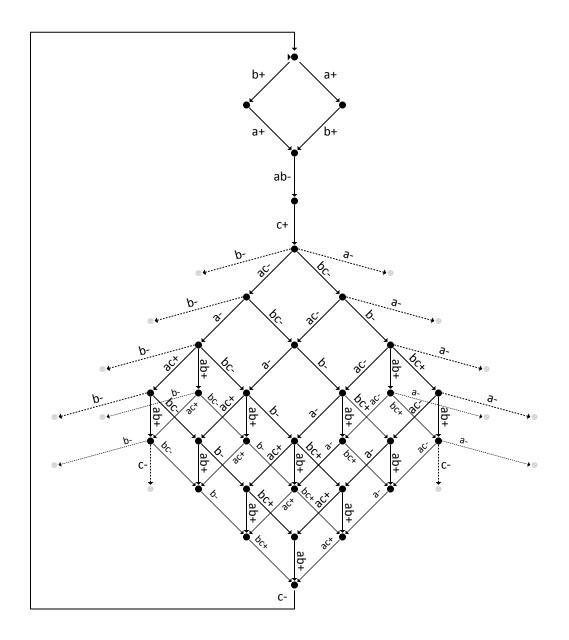

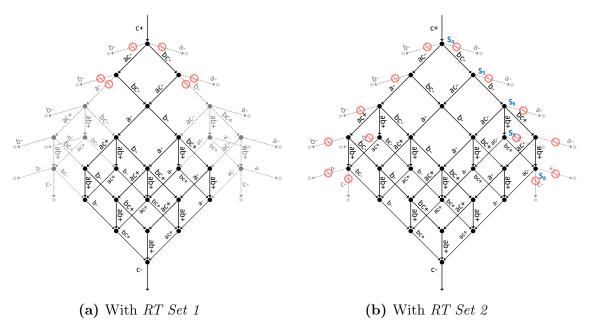

| 3.19 | RT constraint sets comparing old and new definition of semimodularity | 37 |

|------|-----------------------------------------------------------------------|----|

| 3.20 | Snapshot of STG using two different RT sets                           | 38 |

| 3.21 | Example showing the difference between old and new semimodularity     | 39 |

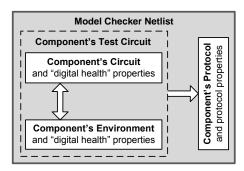

| 4.1  | Model checker overview                                                | 41 |

| 4.2  | Implementation in a model checker                                     | 43 |

| 4.3  | Code for cgate                                                        | 43 |

| 4.4  | Composition of <i>cgate</i> instances to build a C element            | 45 |

| 4.5  | C element with random environment                                     | 46 |

| 4.6  | C element with a closed environment                                   | 47 |

| 4.7  | Code changes for <i>lazy</i> environment                              | 48 |

| 4.8  | Model of a RT constraint                                              | 49 |

| 4.9  | Code for RT constraint module                                         | 50 |

| 4.10 | Code for blocking late events                                         | 50 |

| 4.11 | Example of two paths with a RT constraint                             | 51 |

| 4.12 | Model checking with properties                                        | 51 |

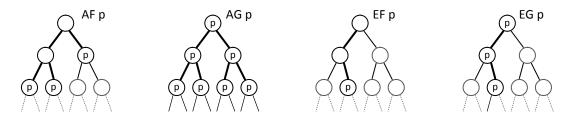

| 4.13 | Basic CTL syntax                                                      | 52 |

| 4.14 | Examples of CTL expression tree                                       | 52 |

| 4.15 | C element specification and properties                                | 53 |

| 4.16 | Alternative properties for the C element                              | 53 |

| 4.17 | Model checking with XDI specification as a monitor                    | 54 |

| 4.18 | STG of C element with error state                                     | 55 |

| 4.19 | Code for the protocol module                                          | 56 |

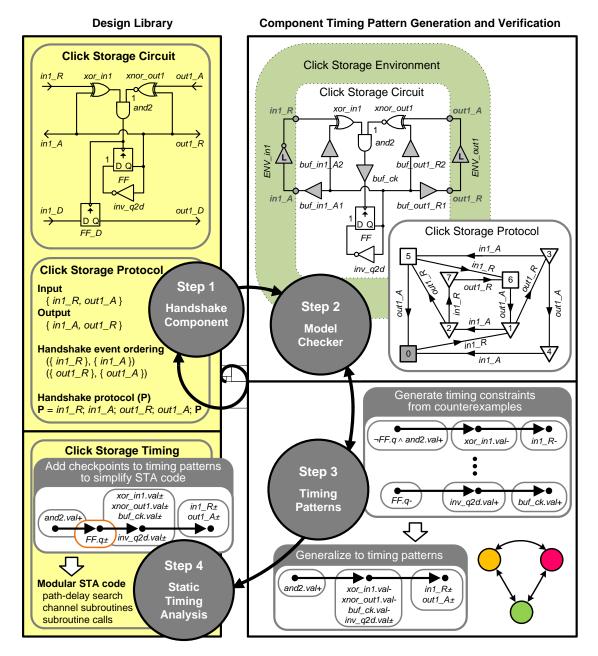

| 5.1  | Reference diagram for ARCtimer                                        | 58 |

| 5.2  | Overview of chip design flow                                          | 60 |

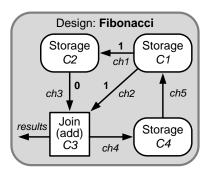

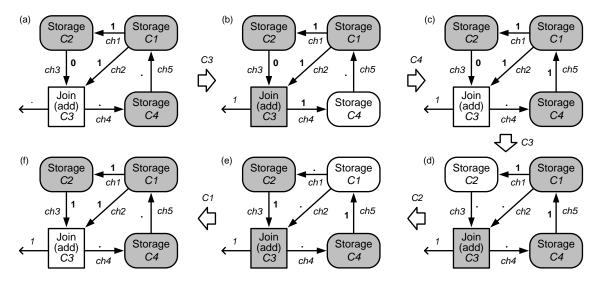

| GUI showing a Fibonacci example                                          | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fibonacci circuit example                                                | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

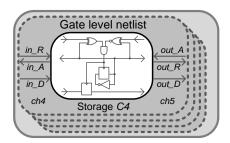

| Gate level netlist                                                       | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

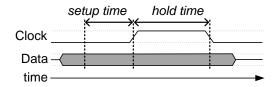

| Setup time and hold time                                                 | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Four main steps of the ARCtimer framework                                | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bundled data and state representations                                   | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

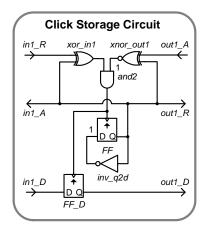

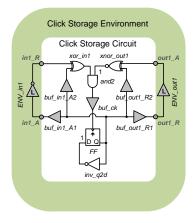

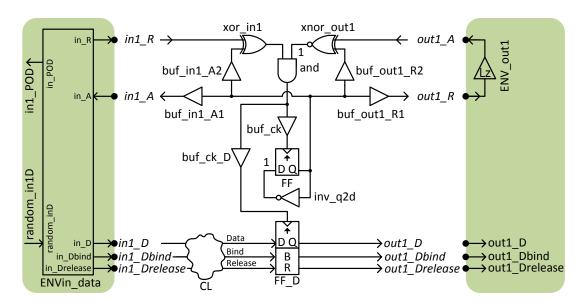

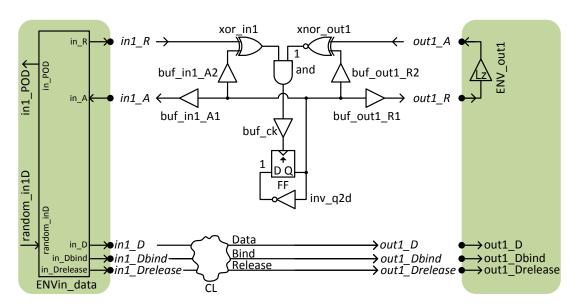

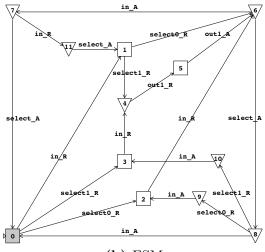

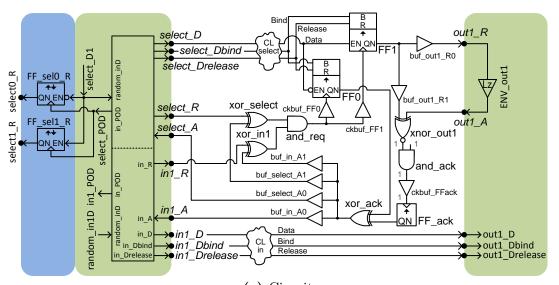

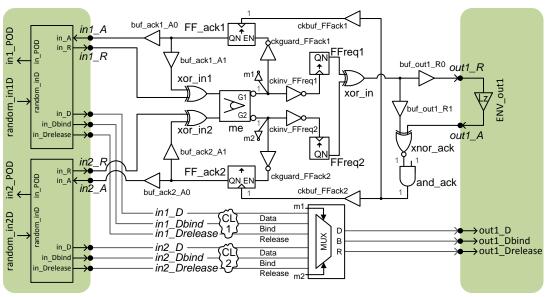

| Click Storage circuit implementation                                     | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

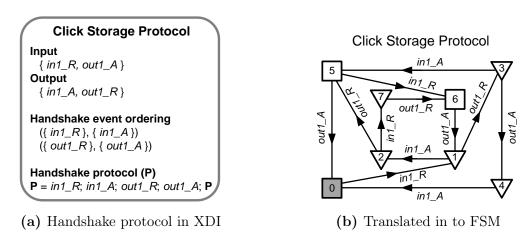

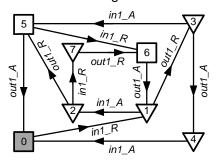

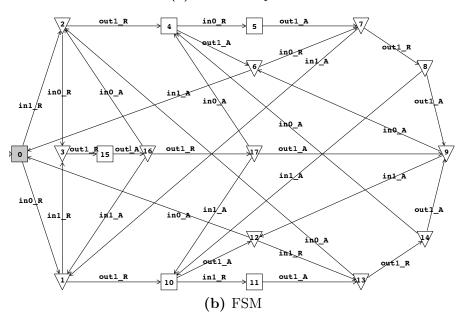

| Click Storage protocol translated to FSM                                 | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

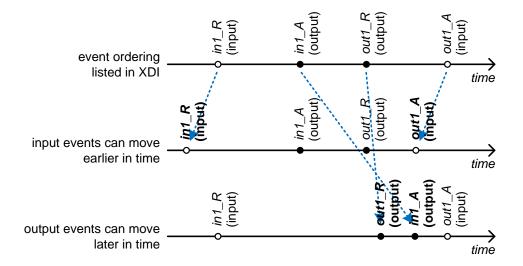

| Possible input and output event orderings                                | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

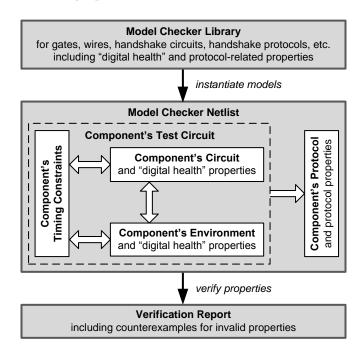

| Organization of model checking task                                      | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DI protocol specification for storage and corresponding code $\ .\ .\ .$ | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

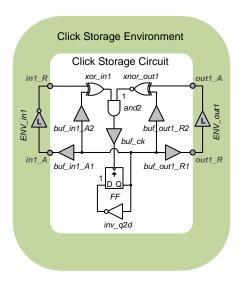

| Click storage circuit and environment                                    | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Code for the circuit                                                     | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

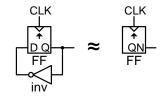

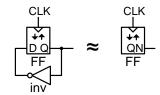

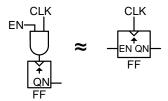

| Code for combinational gate and positive edge triggered FF $$            | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Code instantiating protocol, circuit, and environment                    | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Two counterexamples                                                      | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

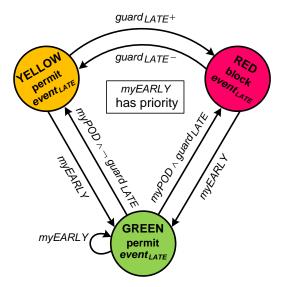

| Stoplight model for RT, and RT set                                       | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Example of applying generalized timing constraint                        | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

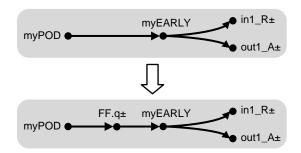

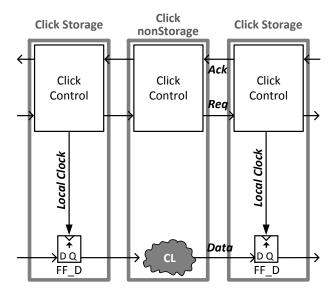

| Timing patterns                                                          | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Code with RT patterns                                                    | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Translation of RT constraint for STA                                     | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

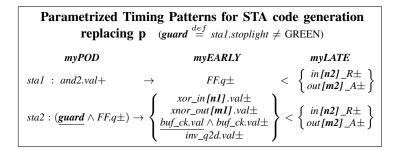

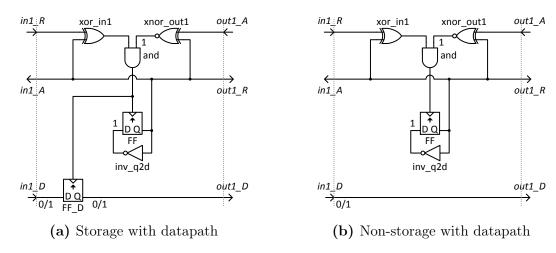

| Click storage and non-storage with datapath                              | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Comparison of bundled-data and bounded-bundled-data                      | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Model of data validity                                                   | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Click storage with datapath                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                          | Gate level netlist Setup time and hold time Four main steps of the ARCtimer framework Bundled data and state representations Click Storage circuit implementation Click Storage protocol translated to FSM Possible input and output event orderings Organization of model checking task DI protocol specification for storage and corresponding code Click storage circuit and environment Code for the circuit Code for combinational gate and positive edge triggered FF Code instantiating protocol, circuit, and environment Two counterexamples Stoplight model for RT, and RT set Example of applying generalized timing constraint Timing patterns Code with RT patterns Translation of RT constraint for STA Click storage and non-storage with datapath Comparison of bundled-data and bounded-bundled-data Model of data validity |

| 6.5  | BBD FF setup constraint                               |

|------|-------------------------------------------------------|

| 6.6  | BBD FF hold constraint                                |

| 6.7  | Code for semimodularity check                         |

| 6.8  | Code for BBD check                                    |

| 6.9  | Code for CL gate                                      |

| 6.10 | Code for FF with data                                 |

| 6.11 | Code for BBD storage circuit                          |

| 6.12 | Code for environment with BBD                         |

| 6.13 | Code to tie in protocol, environment, and circuit     |

| 6.14 | Circuit and environment for BBD storage               |

| 6.15 | Two counterexamples for BBD storage from NuSMV        |

| 6.16 | Circuit and environment for non-storage component     |

| 6.17 | Code for the circuit portion of non-storage component |

| 6.18 | Module main for non-storage                           |

| 6.19 | BBD constraints prepared for STA                      |

## Introduction

## 1.1 Motivation

Modern computer systems are distributed over space. For example, there is the internet of things – a network of physical objects embedded with electronics, software, sensors, and network connectivity, which enables these objects to collect and exchange data. Another example is IBM's TrueNorth [28]. TrueNorth is a system composed of modular chips that act like neurons and form artificial neural networks to run "deep learning algorithms" like Skype's chat translator or Facebook's facial recognition.

Global state is a useful model for traditional clocked hardware, where: state may change only when the clock ticks, where all tasks must fit into the clock period, and where the global state is stable between ticks.

Below follow three examples where events are not simultaneous over space.

The first example relates to the latest planetary mission to Pluto. New Horizons took a picture of Pluto and its moon, Charion. Pluto is very far away – more than 30 times Earth's distance from the Sun. It took about 4 hours to tweak the position of New Horizons to take such a picture. There's a substantial communication delay between earth and Pluto. Clearly, the commands and the photo shot are not simultaneous.

The second example is also from outer space. In August 2012, NASA landed Curiosity on Mars. At the time, Mars was a communication distance of 13 minutes away. During the last 13 minutes of landing, the landing system worked on

autopilot – self-directed, self-controlled, autonomous.

As a third example, let's take a look at something closer and more down to earth. What about chips? What about communication delays within a cubic inch? Even here, down to earth, within a cubic inch of silicon, the communication delay in a network chip with a size of less than a cubic inch are longer than the delays that we use to control the chip. Moreover, the complexity of pretending that events in the chip are simultaneous is huge: hundreds of clock domains, and ten thousands of clock synchronizers [58].

Clearly, the notions of global state and global control fail to scale over space, even within the cubic inch space of a single chip.

With the advance of IC manufacturing technologies, high speed digital systems have grown in complexity. In the past, all digital systems required data to pass sequentially through the system. The standard approach to this was to synchronize the entire system to a common global discrete period clock. This results in synchronous systems that are orchestrated by a centralized clock that operates on a fixed rate. Control and data signals are stored and passed in lockstep on fixed intervals as determined by the clock and its phases. All functions between the storage elements are evaluated during the clock period. This is a valid model as long as the clock period is longer than the time it takes for the clock signal to travel from one end to another end of the circuit, giving a well-defined semantics to the term 'lockstep.'

Thanks to continuous scaling of VLSI to meet the ever-increasing demands for more speed and less power, the clock period has shrunk to below the chip's end-to-end clock traversal time. In addition, in many high-performance designs, clock power has been reported to exceed 30% of the total power consumption [10].

Power is now an additional limiting factor in raising the clock frequency [57]. As a result, the conceptual framework of synchronous design faces new challenges beyond pure functionality and raw throughput, concerning timing closure and power dissipation, process variation and interfacing.

Due to these drawbacks, asynchronous circuits are gaining interest. Asynchronous circuits, also known as self-timed circuits, do not have a global clock. The asynchronous circuits or self-timed circuits communicate with their neighbors through handshake protocols.

Potential advantages of self-timed circuits compared to synchronous circuits are as follows:

## • High speed

Since there is no central clock, there are no clock skew problems. Self-timed circuits can be designed for average performance while synchronous circuits are typically designed for worst case performance.

## • Low power

Self-timed circuits consume power when and where needed. In contrast, synchronous circuits usually have a ticking clock that consumes power even if there is no work to do.

## • Robustness

Self-timed circuits self-adapt to temperature and voltage variation. In contrast, synchronous circuits require clock frequency regulations to track voltage variations.

## • Low electromagnetic interference

The clock pulses on synchronous circuits operating on the exact same frequency generate resonance and electro-magnetic interference (EMI). The irregular behavior in self-timed circuits provides very low EMI.

## Modularity

The asynchronous or self-timed components communicate with each other through handshake protocols. The protocols are implemented locally, with local timing constraints. The locality of time make it possible to build large systems of any scale.

However, there are also drawbacks such as:

### • Different notion of time

The global clock is replaced by handshake protocols.

## • Testability and Debug

Synchronous circuits can simply freeze the clock for better visibility of circuit actions. We recently provided a generic solution to freeze local self-timed actions for test and debug with Mr.GO [39].

## • Lack of EDA tool support

Lack of CAD tool support from EDA industries makes wide adoption of self-timed design hard. The ARCtimer presented in this thesis shows how to provide EDA tool support for timing closure of self-timed systems.

The biggest problems are the lack of a standard work flow, and a non-standard way of designing circuits. A difference in the timing regime requires a different way of thinking of circuit design, which isn't being offered as education in many places. Portland State University is one of the research institutes world wide where students can study self-timed design. Some companies that have adopted self-timed circuit designs have their own design flow and tools which are not publicly available.

This thesis tackles the problem of lacking a standard workflow by providing a general methodology and work flow outline for solving the local timing constraints that support the handshake protocols between self-timed components. This workflow is called ARCtimer.

The near-term goal of ARCtimer is to generate and repair local timing constraints necessary for correct communication through handshaking. Once the handshake protocols can be assumed correct, the remaining and recurring task of building systems out of handshaking circuit components becomes a delay-insensitive design task. Thus, the longer-term goal of ARCtimer is to support the large-scale integration of delay-insensitive circuits. Hence, the title of this thesis.

## 1.2 Problem Definition

In digital circuits, a logic hazard is an unexpected output that lasts temporary after an input has changed. Because hazards are temporary, synchronous circuits can usually clear the hazard by slowing down the clock cycle used for synchronizing such that the correct output is in the right place by the time the active clock edge arrives. Self-timed circuits on the other hand does not have a global clock to delay the sampling of the output. Each component operate on their own pace solely relying on handshake signals to communicate with neighboring components.

Because handshake operations are driven by events, glitches must be avoided.

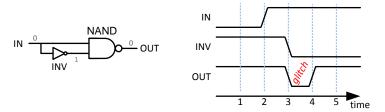

Figure 1.1: An example of combinational logic that could cause a glitch. From the initial state as marked in the Figure, once the IN makes a rising transition (time = 2), INV makes a falling transition (time = 3). The NAND gate seeing both inputs high (between time = 2, 3) produces a momentarily glitch (time = 3), but then recovers (after time = 4).

To make a circuit free of hazards, we look at *delay-insensitive* (DI) circuits which are the most robust of the asynchronous circuit classes. This circuit class operates correctly with unknown delays in wires and gates. But due to heavy restrictions, only a few circuits are truly insensitive to delays of gates and wires. Timing constraints can be applied to make the circuit operate in a DI fashion, but how can one be sure that the timing constraint set is complete? To verify these timing constraints, what kind of tools should one use, and how would one model the system? What kind of timing constraints should one add? Are the constraints placed at optimal locations?

The problem with lack of support from the industry and standardized tools makes it hard to widely adopt self-timed designs. The solutions are not interchangeable and usually don't carry over with technology advancements. Static timing analysis (STA) loop cutting doesn't work with conventional STA tools because they are built for synchronous circuits.

## 1.3 Proposed Approach

The circuit can behave like a delay-insensitive (DI) circuit if each handshake component faithfully follows their specified DI protocols. ARCtimer uncovers the delay sensitivities and defines a delay repair procedure in advance, so that when the component is used the designer and the STA tool know what to analyze and how to repair it, if it fails DI.

We design our circuits using the theory of Logical Effort [56], where we assume gates and wires are well-designed and there are no adverse analog effects. For the handshake component's protocol, we use the formalism of Delay-Insensitive Algebra developed by [14,20,59], which has a compact and complete specification. Delay-Insensitive Algebra specifies both safety property and liveness property, which are important for choices of action.

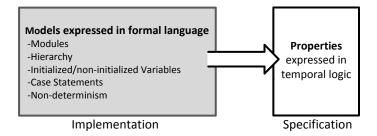

To verify our design, we use a general purpose model checker to perform an exhaustive verification. Each of the component and protocol specification are modeled for the model checker. The properties such as safety and liveness properties come from the protocol specification, and with the help of a model checker, we find a complete set of timing constraints that are required to make the circuit behave like a delay-insensitive circuit. The generated timing constraints capture what is needed to obey the protocol interface.

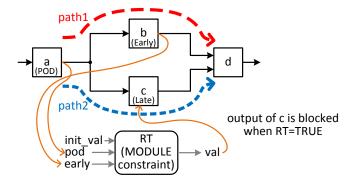

To model timing constraints, we use relative timing methodology [49] which is based on the ordering of events. Although not practical, the glitch would have been avoided in Figure 1.1 if there were a relative timing constraint such as "when IN changes, the INV's output must change before OUT changes." This can be interpreted as "the path from IN to OUT must be slower than the path from IN through INV to OUT." To guarantee that this is always true, a delay exceeding

the amount of delay in the path IN-INV-OUT could be added in the path between IN-OUT.

The complete set of timing constraint is carefully analyzed to form a generalized timing constraint which becomes stored in the design library. For larger components that belong to the same circuit family, one can use a known starter set of timing constraints from the generalized constraints to find the missing timing constraints. Once the design library is complete, designers can use the components without redoing timing verification.

## 1.4 Contributions

This work is relevant for designing self-timed circuits that use timing constraints. In practice, very few self-timed circuits can work without timing constraint [16,22].

We developed *ARCtimer*, a framework of formal modeling and verification methods for generating and verifying timing constraints for handshake components with bounded-bundled-data protocol. Through this framework, we can uncover what is needed to make the component's gate-level circuit follow the component's handshake protocol.

Our focus was to ensure that not only the circuit obeys the handshake protocol but also its timing constraints and static timing analysis code are sufficiently general for use in a design library. To achieve this, we analyzed the design patterns and generalized the timing constraints into timing constraint patterns which are also more intuitive.

We build up a shared understanding of what a framework like ARCtimer entails, and helps readers understand the tradeoffs and decisions, and identify essential decision points, the choices one can make, what we and others chose, and why. We have exchangeable solutions in three areas: STA loops kept intact, DI protocol specifications, failure analysis heuristics to derive timing constraints.

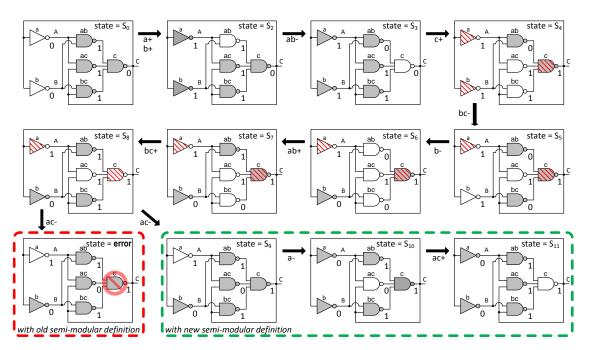

We explain how to model each component, how to model the protocol into properties in a model checker. While doing so, we found that there is a conflict between the design paradigm of semimodularity used since the early days and the new paradigm of relative timing introduced recently to make self-timed circuits fast and efficient. We show this conflict by redefining semimodularity in a way that fits rather than fight relative timing. This work was published in [32].

The model checker we use is a general purpose tool which is open to public access. The use of a specialized tool for timing verification for self-timed circuits carry hidden assumptions. Custom tools are also less flexible in case a user wants to add new features.

Following is a list of contributions from this thesis:

- 1. Upfront modeling on a component by component basis to reduce the validation effort required to:

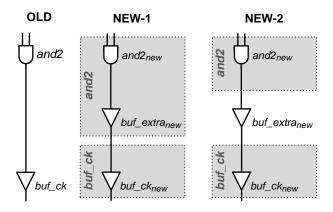

- (a) reimplement components in different technologies, by using the notion of patterns seen in Chapter 5, Section 5.2.3.3 and Figure 5.20

- (b) assemble components into systems as shown in Chapter 5, Section 5.1.2 and Figure 5.3, and

- (c) guarantee system-level timing closure by using ARCtimer introduced in Chapter 5, Section 5.2 and Figure 5.7.

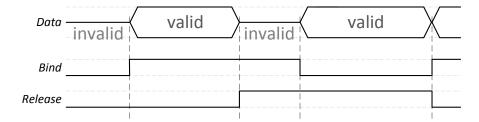

- 2. Modeling of data and bounded-bundled-data timing constraints that permit the control signals to lead or lag behind data signals to optimize system timing. This is shown in Chapter 6, Figure 6.2.

3. New semimodular model [32], a key property present in most self-timed modeling tools such as [30,47,63]. The enhanced definition of semimodularity can be found in Chapter 3, Section 3.7.2 and Definition 3.7.2.

I have published the following papers:

## 1. Journals

- (a) H. Park, A. He, M. Roncken, and X. Song. Semi-Modular delay model revisited in context of relative timing. IET Electronics Letters, 51(4):332–334, 2015 [32]

- (b) H. Park, A. He, M. Roncken, X. Song, and I. Sutherland. Modular timing constraints for delay-insensitive systems. JCST, Springer, accepted 2015 [33]

#### 2. Conferences and Poster sessions

- (a) M. Roncken, S. Metta Gilla, H. Park, N. Jamadagni, C. Cowan, and I. Sutherland. Naturalized communication and testing. In Asynchronous Circuits and Systems (ASYNC), 2015 21st IEEE International Symposium on, pages 77–84, May 2015 [39]

- (b) H. Park, A. He, M. Roncken, X. Song. Verifying Timing Constraints for Delay-Insensitive Circuits. Poster presentation. In Asynchronous Circuits and Systems (ASYNC), 2015 21st IEEE International Symposium, May 2015.

- (c) M. Faust, H.Chung, H. Park, J. Rodriguez. Introducing hardware emulation in the ECE curriculum. In IEEE International Conference on Microelectronic Systems Education (MSE '11), pages 39–40, June 2011.

## 1.5 Organization of the Dissertation

The rest of the dissertation is organized in seven chapters.

Chapter 2 reviews related work on self-timed circuit verification.

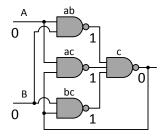

Chapter 3 describes the basic fundamentals of asynchronous circuits, delay models, circuit and environment model, and relative timing methodology. An enhanced definition of semimodularity is presented with an example of a C-element.

Chapter 4 describes how modeling and verification is done in a general purpose model checker using a C-element as an example.

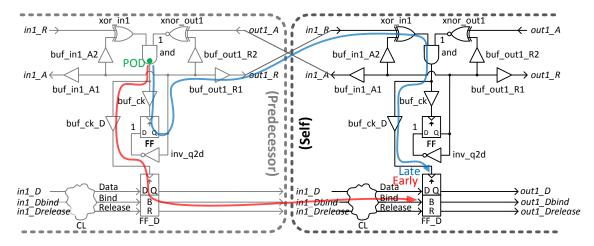

Chapter 5 presents ARCtimer, our timing verification framework for generating and verifying delay-insensitive circuits. A storage element from Click circuit family is used as an example. We show how relative timing constraints are derived and modeled, and then generalized into timing patterns.

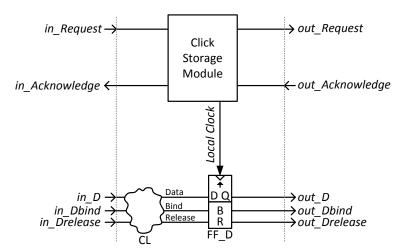

Chapter 6 adds datapath to the storage example and show how data is modeled, and what type of timing constraints are required for the bounded-bundled-data protocol.

Chapter 7 concludes this thesis and addresses possible future work.

#### Related Work

Timing closure for self-timed digital circuits is a problem of a high relevance, because very few circuits, if any, are insensitive to wire and gate delays [16, 22]. Several approaches have been proposed to tackle timing verification.

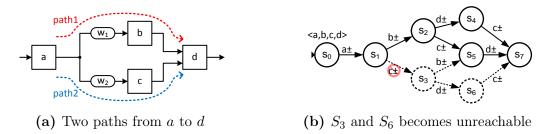

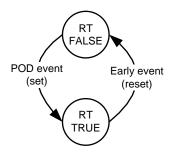

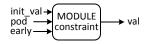

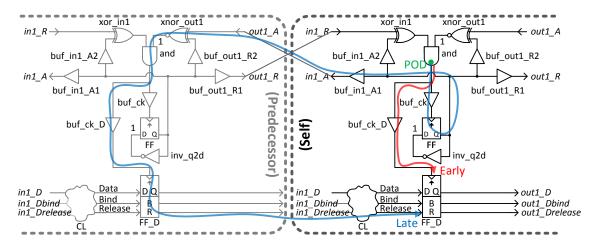

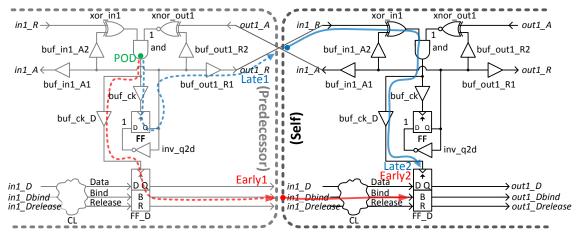

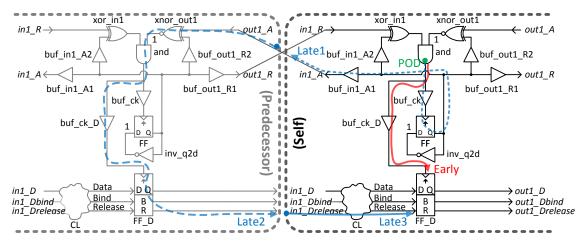

Kenneth Stevens et al. in [50] introduced Relative Timing (RT) methodology for synthesis and also for verifying asynchronous circuits that use unbounded delay model. Relative timing constraints the overall delay of two paths such that a specified path is faster than the other. The two paths has a common starting point, which is called Point-Of-Divergence (POD), and has two different ending points, called Point-Of-Convergence ( $POC_0$  and  $POC_1$ ). The RT constraint shown in Figure 2.1 reads as "if event POD happens, event  $POC_0$  must happen before event  $POC_1$ ." See Section 3.6.

$$POD \rightarrow POC_0 \prec POC_1$$

**Figure 2.1:** RT constraint is expressed as a path from point-of-divergence (POD) to two different point-of-convergence (POC). From POD, the delay of the path to  $POC_0$  must be less than the path to  $POC_1$ .

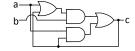

Relative timing methodology makes timing requirements explicit. Timing requirements of a circuit can be directly added, removed, and optimized using this style. When used for synthesis, depending on the environment, the circuit can be simplified with RT constraints since it reduces concurrency in the implementation. Figure 2.2b from [50] shows an example of a simplified C element with the assumption that the environment always changes input a from high to low before b changes from high to low.

- (a) Speed-independent C-element

- (b) With assumption  $a \prec b -$

**Figure 2.2:** Simplification in synthesis. Timing assumptions of the environment can lead to a simpler circuit as shown in [50].

For verification, they use a custom verification tool called Analyze which use trace semantics and calculus for communicating system (CCS) based logic conformance relation [48]. They model and verify that the timing-constrained circuit meets the protocol. The application of timing constraints can be aggressive or conservative depending on the application.

Yang Xu [62,63] builds upon [18] and [50]. He created a tool called ARTIST which automatically generates timing constraints based on bisimulation formalism. Error traces or action sequences are evaluated and a RT constraint is generated and added to the circuit implementation. The tool iterates through evaluation and generation of RT constraints until the circuit implementation conforms to the specification. However, automation typically pushes constraints to become too fine grain to provide intuition. Also, the constraints are technology dependent.

Krishnaji Desai *et al.* in [9] models the circuit and RT constraints in NuSMV model checker to check for correctness. They demonstrate the growth of the system size as pipeline stages become deeper. However, progress and choice equivalence properties are absent from the NuSMV based timing verification work.

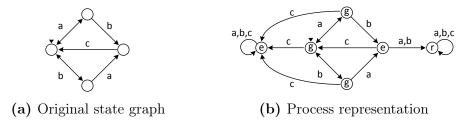

Radu Negulescu *et al.* in [30,31] in Process Spaces and FIREMAPS built a system very much like Ken's. The difference is that they use complete path of events as constraints instead of start and end points of a path. Their research are examples that use the theory of *Delay-Insensitive Algebra* for both modeling and verification task.

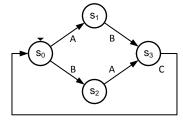

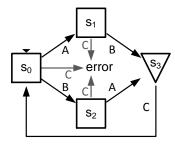

**Figure 2.3:** Constructing a process representation using Delay-Insensitive Algebra as shown in [30]. The state machine needs to be a complete automaton so in addition to the original state graph, they add reject state  $((\hat{r}))$ , error state  $((\hat{e}))$ , and goal states  $((\hat{g}))$ . An error from the environment leads to a reject state where it can't escape while an error from the circuit leads to an error state which it can't escape.

We use a similar approach for describing the specification of the protocol when expanding the state graph. We have two types of error states, error from the environment and error from the circuit. For the timing constraints, they use a term called *Chain Constraint* which is a path based constraint. The path is expressed with all the intermediate events on the path, listed like a chain, which the delays to the early and late events are calculated. Chain constraints are much easier to translate into STA code than relative timing constraints. However, chain constraints are also much harder to model in a model checker than relative timing constraints. We add checkpoints in our path of relative timing constraints to perform STA.

Prasad Joshi [15] verified single track bi-directional wires for the GasP component, and worked on handling loops for STA tools by breaking timing loops. Since conventional STA flow does not support bi-directional wires, he split these wires to verify GasP circuit family. He applied RT constraints on the control logic to satisfy the specification.

Yoneda et al. in [64] uses metric timing. Using absolute delay reduces complexity in state space, and they suggest that un-timed circuits may introduce

unrealistic failure traces complicating the verification process. They model each circuit element with a time Petri net. Using min—max delay is a different approach, however, this seems to fit less with self-timed design compared to relative timing. This method also makes the constraints technology dependent.

Khaled Alsayeg et al. in [1] created Requirement Analysis Tool (RAT) to formally verify asynchronous circuits using model checking techniques. The tool checks for the correctness of the behavior using *Property Specification Language* (PSL). They describe the circuit using a set of properties expressed in temporal logic, and use a model checker to verify the properties. They start with specifying properties for a general gate model, and then move to abstract level and check the interconnection of each block.

## Fundamentals and Semi-modularity Revisited

Self-timed circuits, also known as asynchronous circuits, operate on a handshake protocol and communicate through channels with their neighbor modules. Ensuring that each module operates correctly according to the handshake protocol, one can easily build scalable systems from these self-timed components. We build our self-timed designs from circuit components that interact using handshake protocols. The designs that we consider are delay-insensitive as long as every component faithfully follows the handshake protocols. By carefully considering time locally, we can ignore time globally. We use Relative Timing (RT) methodology [9,62] and build upon it to enforce local timing relations as known as RT constraints.

This chapter introduces the basics of communication protocols, graphical representation of circuits, gate and wire models, coloring schemes. We also discuss definitions of semimodularity, and bring in an enhanced definition of semimodularity used in the presence of RT constraints, and show by example of a Muller C element how the enhanced definition is applied.

## 3.1 Asynchronous Communication Channels

Contrary to synchronous circuits where every action happens on a beat of a clock, asynchronous circuits communicate with neighbors through communication channels with the use of handshakes. This can be thought of as an interaction between two people, one person sending a request as needed, and the other person acknowledging the request at his own pace. In synchronous system, these two

people would only be able to communicate during the tick of a clock, and the clock would keep ticking even when there is no real work going on.

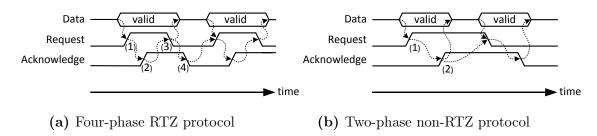

Bundled-data four-phase and two-phase handshakes are widely used handshake protocols. Bundled-data refers to data wires being bundled with a separate request and acknowledge wires. The four-phase and two-phase naming comes from the number of transitions required in the request and acknowledge wires to complete a handshake event.

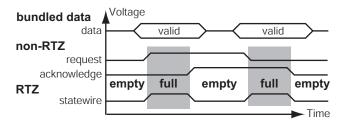

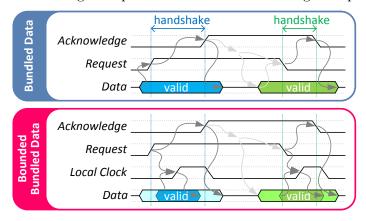

Figure 3.1: Timing diagram of bundled data handshake protocols.

Four-phase handshake: (1) The sender places the data and sends a request signal and valid data. (2) The receiver detects this received data, and acknowledges. (3) The sender responds to the acknowledgement by lowering the request signal, and by generating new data. (4) The receiver acknowledges this and lowers the acknowledge signal. <sup>1</sup>

Two-phase handshake: (1) The sender places valid data and sends a request signal. (2) The receiver receives the data and acknowledges.

In digital circuits, the voltage level of a wire is represented with Boolean value 0 or 1, for low and high respectively. A transition on a wire means the voltage level changed from low to high, or high to low. Comparing the four-phase to the two-phase non-return-to-zero handshake protocol, the four-phase protocol has the advantage of simpler circuitry in that it uses level signaling for the control and

<sup>&</sup>lt;sup>1</sup>Various data validity schemes exist. See Ad Peeters 1996 Ph.D. dissertation [35] for details.

allows each state to be unique, making it easy to determine the initial state of each handshake. Its disadvantage is the extra return-to-zero (RTZ) transitions which take extra time and power. The two-phase handshake protocol could lead to a faster circuit since there are fewer signal transitions, but the circuit is typically more complex.

#### 3.2 Circuit Class

Asynchronous circuits can be classified by their delay model. In this thesis, unbounded delay means a positive but possibly infinite delay, while bounded delay means a positive but finite delay. Muller's *Speed-Independent* (SI) circuits [29] with an example in Figure 3.2a use an unbounded delay model on the gates. Known as *iso-chronic forks*, either the wires are assumed to have negligible delay, or the wire delays are lumped into the gate which it connects to. In result, when a gate's output changes, all the connected gates immediately sees the change.

Delay-Insensitive (DI) circuits which are the most robust of the three classes do not make any delay assumptions and operate correctly under arbitrary gate and wire delays. This is shown in Figure 3.2b where each gate and wire has its own delay.

The delay model of *Quasi-Delay-Insensitive* (QDI) circuits differ from the SI model in that different branches of a forked wire may have different delays. This means that certain forks are iso-chronic.

**Figure 3.2:** Circuit classification depending on the delay model. Square blocks represent gate delay and round blocks represent wire delay.

Very few circuits are DI or even QDI or SI. In general, relative timing constraints are needed on top of these circuits to enable the user to repair the delays to make it behave according to the protocol.

We model our circuits for higher-level delay-insensitive protocol applications where the correctness is independent of gate and wire delays in the sense that we can repair any given gate and wire delay setting to obtain correctness of the application.

## 3.3 Graphical Representation of Asynchronous Circuits

Asynchronous circuits must be free of hazards, so every gate or wire transition counts and carries a meaning. To express the possible behaviors of the circuit, we use a finite state machine with interleaving semantics, where each node is a unique vector of logic wire levels. A module's communication protocol describes the behavior at a more abstract level and only sees the external inputs and outputs.

Such state machines can be represented as a directed graph using a 4 tuple  $G = \langle S, s_0, E, T \rangle$  as in Figure 3.3b:

- S: Finite set of nodes represented with circles

- $s_0$ : A set of initial node  $\in S$

- E: Event, which is a wire transition from low to high, high to low, or simply any transition

- $T: \{S \times E \to S\}$ : Transition is labeled with an event, leading to a next state. We use interleaving model where only single event happens in a transition

A wire *transition* indicates a change in the logic level of the wire. We use the following notation for transitions:

- +: low-to-high transition

- -: high-to-low transition

- ±: either low-to-high or high-to-low transition

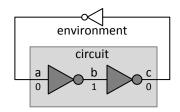

Let's now look at the system shown in Figure 3.3a. The system part called "circuit" has two inverters connected in series and the system part called "environment" has one inverter. The wires are initialized as a=0, b=1, c=0. After the environment circuit changes a from 0 to 1, it produces the next input only after it sees an output transition on output of c the circuit. A state is defined as < a, b, c>, and this system can be modeled with 6 states total if we distinguish up and down transitions. From the initial state  $s_0 = < 0, 1, 0>$ , both inverters are stable (colored gray). The only possible action is for the environment to issue a+, and go to state  $s_1 = < 1, 1, 0>$ . Note that there are no states with < 0, 0, 0> or < 1, 1, 1> since these states are not possible in this environment.

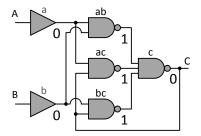

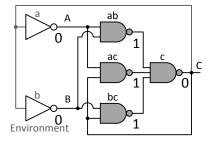

- (a) Two inverters with environment

- (b) State graph,  $s = \langle a, b, c \rangle$

Figure 3.3: Example of two inverters in series and its state graph.

## 3.4 Gate and Wire Model

A gate is represented by a Boolean function. We use the theory of Logical Effort [56]. As a result, our circuits come with an "analog health" waiver: their signal rise and fall times are sufficiently good to skip analog circuit analysis.

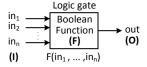

A logic gate is modeled as a triple  $\langle I, O, F \rangle$  where:

- *I* is a set of input signals

- O is an output signal

- F is a set of the circuit functions, where after an unbounded delay, O receives the value of F

Figure 3.4: Representation of a logic gate.

A stable gate means F(I) and O have the same value, and that there is no transition scheduled on the output. We color stable gates gray.

$$out = F(in_1, ..., in_n)$$

(stable)

When F(I) has a different value from O, O may change to the value of F(I). We color unstable gates white.

$$out \neq F(in_1, ..., in_n)$$

(unstable)

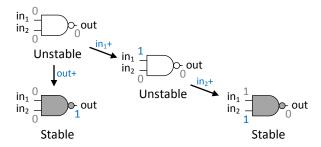

Let's look at an example of a two-input NAND gate shown in Figure 3.5. The function of the gate is expressed as  $F(in_1, in_2) = \neg (in_1 \wedge in_2)$ . When  $in_1 = 0$  and  $in_2 = 0$ , the function  $F(in_1, in_2)$  is  $\neg (0 \wedge 0)$ . In this state, if the current output out is 0, this gate is unstable. If the current output out is 1, then this gate is stable. This is shown in Figure 3.5b. The coloring scheme of stable and unstable will be used throughout this thesis only where necessary.

| $in_1$ | $in_2$ | $F(in_1, in_2)$    | out | Stable |

|--------|--------|--------------------|-----|--------|

| 0      | 0      | $\neg (0 \land 0)$ | 0   | False  |

| 0      | 0      | $\neg (0 \land 0)$ | 1   | True   |

| 0      | 1      | $\neg (0 \land 1)$ | 0   | False  |

| 0      | 1      | $\neg (0 \land 1)$ | 1   | True   |

| 1      | 0      | $\neg(1 \land 0)$  | 0   | False  |

| 1      | 0      | $\neg(1 \land 0)$  | 1   | True   |

| 1      | 1      | $\neg(1 \land 1)$  | 0   | True   |

| 1      | 1      | $\neg(1 \land 1)$  | 1   | False  |

(a) 2-input NAND gate

(b) Example of unstable and stable

**Figure 3.5:** 2-input NAND gate truth table showing all 8 states, and an example of unstable and stable gates.

As shown in Figure 3.6, an *unstable* gate that is given enough time will eventually become *stable* by changing its output. However, it is also possible that the inputs changes quickly enough that the gate no longer wants to change the output, as it considers itself *stable*. Such example is possible in an inertial delay model.

**Figure 3.6:** Unstable gate may become stable by changing the output (left path), or by changing the inputs (right path).

An inertial delay model can be thought of as a logic gate model with inertia. Inputs have to hold long enough to propagate to the output. Short pulses may be ignored if the pulse is too short.

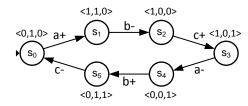

Figure 3.7 shows all possible actions for a 2-input NAND gate under such an inertial delay model. For example, trace  $s_0 \xrightarrow{a+} s_1 \xrightarrow{b+} s_3 \xrightarrow{b-} s_1$  shows that in state  $s_3$ , b was retracted too quickly that it wasn't propagated to the output. This trace can also be seen as the gate becoming unstable in state  $s_3$ , but because input b changed quickly back to 0, the gate became stable again.

**Figure 3.7:** Inertial delay model shows that inputs can be withdrawn at any time even before it propagates to the output.

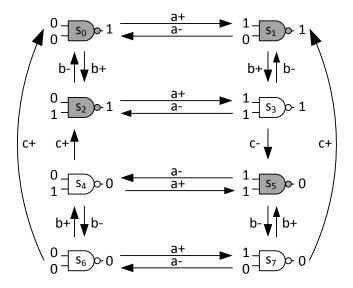

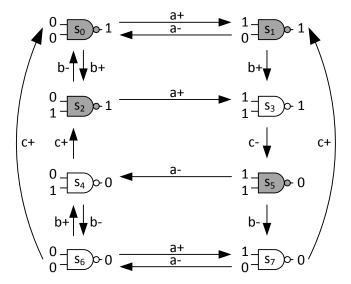

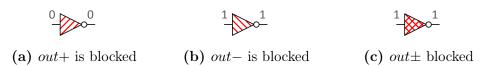

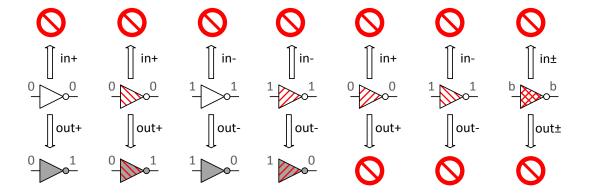

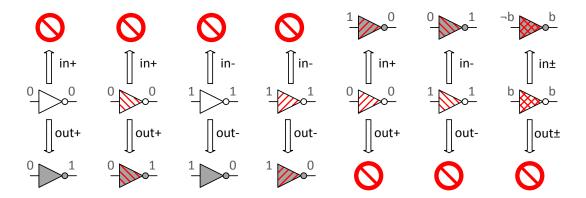

Semimodular delay model introduced by David Muller [29], and brought to the attention of a wider audience through Raymond Miller's 1956 book [27] is widely used for designing hazard-free self-timed circuits by insisting that a digital signal changes occur before being disabled. One might call it the "no change left behind" paradigm. Once an output change is scheduled, it must go through. This puts a strong restriction on the inputs and the surrounding environment. Figure 3.8 shows all possible actions that are allowed in a semimodular delay model for a 2-input NAND gate. Compared to the inertial delay model in Figure 3.7, there are four fewer possible transitions which are prohibited because the pending output change on c from state  $s_3$  and  $s_7$  cannot be canceled. From an unstable state  $s_5$ , the only possible action is to change the output by doing c— and going to state  $s_5$ . From another unstable state  $s_7$ , as long as the input change doesn't make the gate stable, it is allowed to take that action, which is why going to state  $s_6$  by a— is legal.

**Figure 3.8:** Semimodular delay model shows that when an output change is scheduled, it cannot be canceled by changing an input. This is seen in state  $s_3$  where it cannot do a— or b—. In state  $s_4$ , action a+ is not possible, and in state  $s_7$ , action b+ is not possible.

Transport delay model which is also used with inertial delay model in hardware description language during functional simulation assumes that no matter how short a pulse is, it is scheduled and propagates to the output. Transport delay model is used for functional simulation and timing analysis, and it is typically used with fixed delay range. Semimodular model is a logic model used for logic simulation and verification analysis of arbitrary delay range, but other than that they express the same thing but used for different purpose.

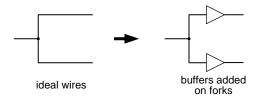

Wire delays are making a bigger presence on the circuit with advances in process technology. The wire delays on different paths of a fork can't be ignored. To model the difference in wire delay on forks, buffer gates are added in each wire branch as done in [46].

Figure 3.9: Buffers are added to model delays in the branches of forked wires

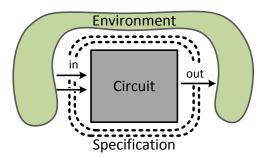

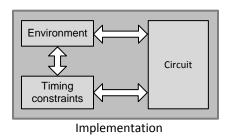

## 3.5 Environment Model

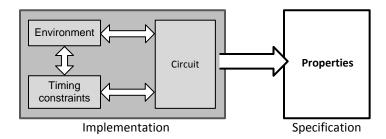

Every component operates in some environment which provides the inputs. Overcomplicating the environment leads to unnecessary computation, while oversimplifying will not accurately model the real environment. There are basically two modes of operation of the environment, fundamental mode pioneered by [13], and input-output mode pioneered by [29]. Both modes assume that the circuit starts in a stable state. Fundamental mode allows the environment to change one input, and waits until the entire circuit is stable. Only then can it change the next input. Input-output mode allows to change the inputs, and when the circuit

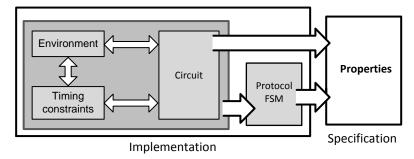

responds by producing any output, the next inputs can be changed again. This means there could be internal signals that are not yet stable before another input changes.