Portland State University PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

10-27-1994

# High Level Preprocessor of a VHDL-based Design System

Karthikeyan Palanisamy Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Electrical and Computer Engineering Commons Let us know how access to this document benefits you.

# **Recommended Citation**

Palanisamy, Karthikeyan, "High Level Preprocessor of a VHDL-based Design System" (1994). *Dissertations and Theses.* Paper 4776. https://doi.org/10.15760/etd.6660

This Thesis is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

# THESIS APPROVAL

The abstract and thesis of Karthikeyan Palanisamy for the Master of Science in Electrical and Computer Engineering were presented October 27, 1994, and accepted by the thesis committee and the department.

COMMITTEE APPROVALS:

# ABSTRACT

An abstract of the thesis of Karthikeyan Palanisamy for the Master of Science in Electrical and Computer Engineering presented October 27, 1994.

# Title:HIGH LEVEL PREPROCESSOR OF A VHDL-BASED DESIGN SYSTEM

This thesis presents the work done on a design automation system in which high-level synthesis is integrated with logic synthesis. **DIADES**, is a design automation system developed at PSU, starts the synthesis process from a language called **ADL**. The major part of this thesis deals with transforming the **ADL** -based **DIADES** system into a **VHDL** -based **DIADES** system. In this thesis I have upgraded and modified the existing **DIADES** system so that it becomes a preprocessor to a comprehensive **VHDL** -based design system from Mentor Graphics.

The high-level synthesis in the **DIADES** system includes two stages: data path synthesis and control unit synthesis. The conversion of data path synthesis is done in this thesis. In the **DIADES** system a digital system is described on the behavioral level in terms of variables and operations using the language **ADL**. The digital system described in **ADL** is compiled to a format called **GRAPH** language. In the **GRAPH** language the behavior of a digital system is represented by a specific sequence of program statements. The descriptions in the **GRAPH** language is compiled to a format called **STRUCT** language. The system is described in the **STRUCT** language in terms of lists of nodes and arrows. The main task of this thesis is to convert the descriptions in the **GRAPH** language and the descriptions in the **STRUCT**  language to the VHDL format. All the generated VHDL Code will be Mentor Graphics VHDL format compatible, and all the VHDL code can be compiled, simulated and synthesised by the Mentor Graphics tools.

# HIGH LEVEL PREPROCESSOR OF A VHDL-BASED DESIGN SYSTEM

by

# KARTHIKEYAN PALANISAMY

A thesis submitted in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE in ELECTRICAL AND COMPUTER ENGINEERING

Portland State University 1994

# TABLE OF CONTENTS

| CHAPTERPAGE    |                                   |    |  |

|----------------|-----------------------------------|----|--|

| 1              | INTRODUCTION                      | 1  |  |

|                | 1.1 DIADES                        | 1  |  |

|                | 1.2 VHDL based DIADES             | 4  |  |

| 2              | DIADES DESIGN AUTOMATION SYSTEM   | 7  |  |

|                | 2.1 Introduction                  | 7  |  |

|                | 2.2 Data Path Synthesis           | 9  |  |

|                | 2.3 Control Unit Synthesis        | 10 |  |

| 3              | ADL HARDWARE DESCRIPTION LANGUAGE | 12 |  |

|                | 3.1 Introduction                  | 12 |  |

|                | 3.2 Program Structure             | 15 |  |

|                | 3.3 Declarations                  | 16 |  |

|                | 3.4 Variables                     | 18 |  |

|                | 3.5 Constants                     | 23 |  |

| 3.6 Identities |                                   | 23 |  |

|                | 3.7 SYMB List                     | 24 |  |

|                | 3.8 Subroutines                   | 25 |  |

|                | 3.9 Statements and Expressions    | 27 |  |

|                | 3.10 Control flow statements      | 42 |  |

|   | 3.11 Special statements                          | 2<br>53 |

|---|--------------------------------------------------|---------|

|   | 3.12 Parallel program execution                  | 57      |

| 4 | GRAPH LANGUAGE                                   | 64      |

|   | 4.1 Introduction                                 | 64      |

|   | 4.2 Coplisset list                               | 65      |

|   | 4.3 Nalisset List                                | 70      |

|   | 4.4 Plisset List                                 | 72      |

|   | 4.5 Nolisset List                                | 72      |

| 5 | STRUCT LANGUAGE                                  | 82      |

|   | 5.1 Introduction                                 | 82      |

|   | 5.2 Syntax of VARLISTA                           | 83      |

|   | 5.3 Syntax of NODLISTA                           | 83      |

|   | 5.4 Syntax of COPLISTA                           | 87      |

|   | 5.5 Syntax of PLISOUT                            | 88      |

|   | 5.6 Syntax of NALISIMP                           | 89      |

| 6 | VHDL TO ADL COMPARISON                           | 97      |

|   | 6.1 Introduction                                 | 97      |

|   | 6.2 The features that are in ADL but not in VHDL | 98      |

|   | 6.3 The features that are in VHDL not in ADL     | 102     |

|   | 6.4 Why VHDL was chosen                          | 107     |

| 7 | COMPILATION OF GRAPH LANGUAGE TO VHDL            | 110     |

|   | 7.1 Introduction                                 | 110     |

| 7.2 Conversion of GRAPH to VHDL          | 3<br>110 |

|------------------------------------------|----------|

| 8 COMPILATION OF STRUCT LANGUAGE TO VHDL | 120      |

| 8.1 Introduction                         | 120      |

| 8.2 Conversion of STRUCT to VHDL         | 120      |

| 9 CONCLUSIONS                            | 131      |

| REFERENCES                               | 133      |

# LIST OF FIGURES

| FIGUREPAGE                              |    |  |

|-----------------------------------------|----|--|

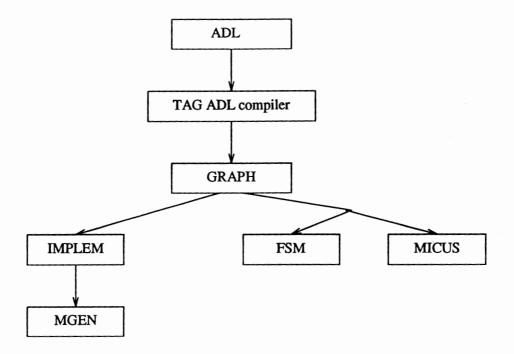

| 1. DIADES system                        | 3  |  |

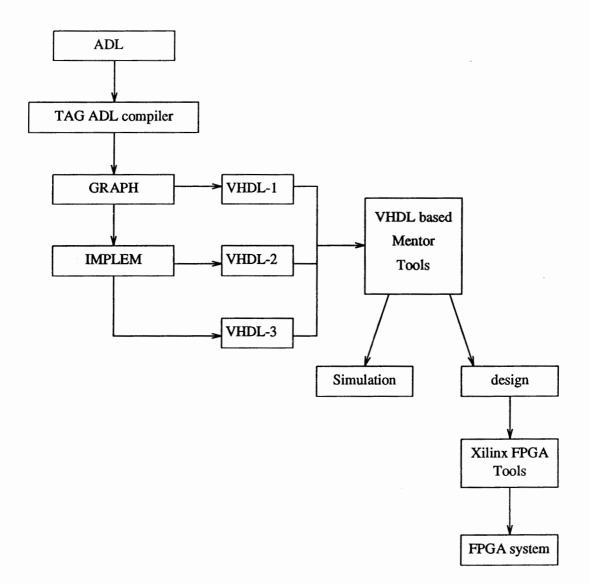

| 2. VHDL linked DIADES system            | 5  |  |

| 3. Current DIADES system                | 8  |  |

| 4. Flow graph for example 3.9.A.1       | 29 |  |

| 5. Transfer of values between variables | 33 |  |

| 6. Transfer of values between variables | 33 |  |

| 7. Concatenation operation              | 35 |  |

| 8. Concatenation operation              | 35 |  |

| 9. Concatenation with bit fields        | 36 |  |

| 10. Logical operation                   | 40 |  |

| 11. Logical operation                   | 40 |  |

| 12. Flow graph for example 3.10.A.1     | 45 |  |

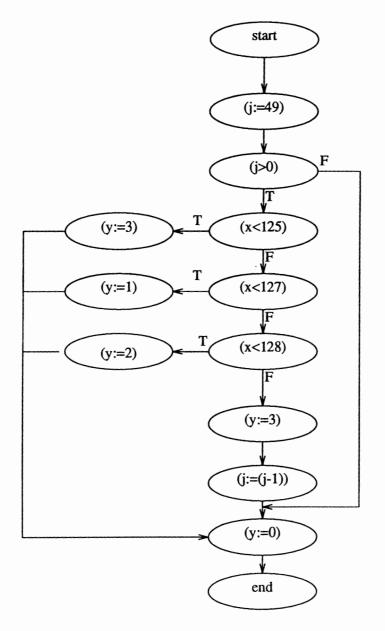

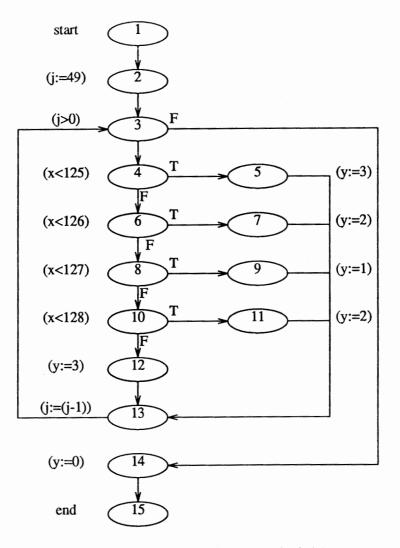

| 13. Flow graph for example 3.10.B.1     | 48 |  |

| 14. Flow graph for example 3.10.C.1     | 50 |  |

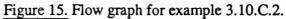

| 15. Flow graph for example 3.10.C.2     | 52 |  |

| 16. Flow graph for example 3.10.D.1     | 54 |  |

| 17. Flow graph for example 3.12.1       | 61 |  |

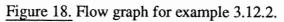

| 18. Flow graph for example 3.12.2       | 63 |  |

| 19. Flow graph for example 4.2.1                | 2<br>67 |

|-------------------------------------------------|---------|

| 20. Flow graph for example 4.2.2                | 68      |

| 21. Flow graph for example 4.2.3                | 70      |

| 22. Flow graph for example 4.5.1                | 76      |

| 23. Flow graph for example 4.5.1                | 81      |

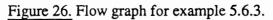

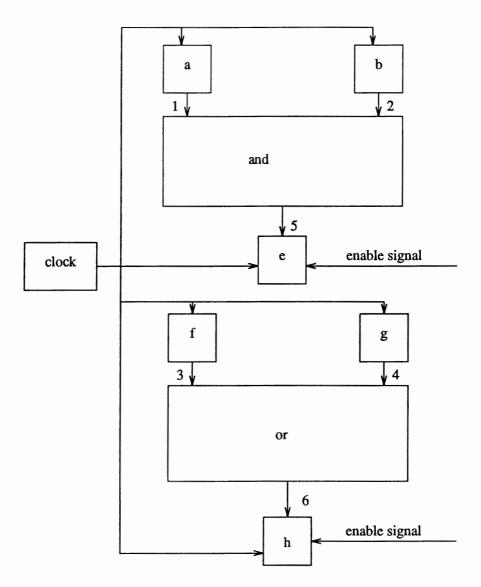

| 24. Graphical representation of example 5.5.2   | 91      |

| 25. Flow graph for example 5.5.2                | 92      |

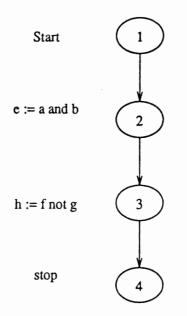

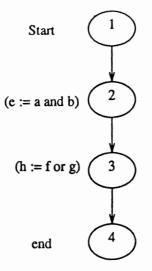

| 26. Flow graph for example 5.5.3.               | 94      |

| 27. Graphical representation of the struct file | 96      |

| 28. Flow graph for example 7.6.                 | 118     |

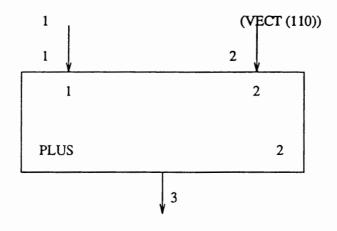

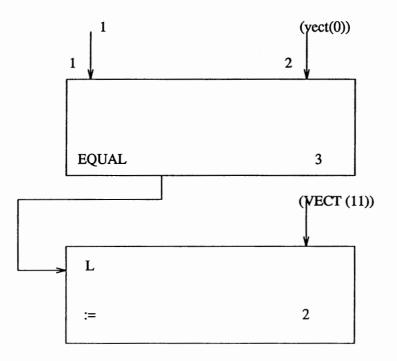

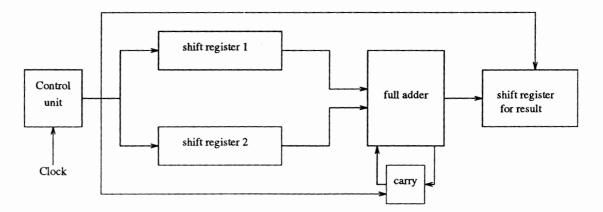

| 29. Addition operation                          | 124     |

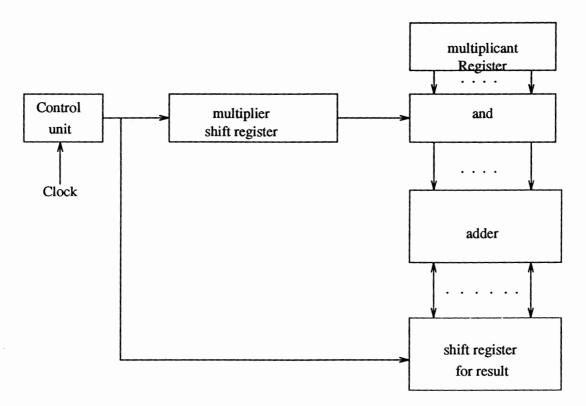

| 30. Multiplication operation                    | 125     |

# CHAPTER I

#### INTRODUCTION

In recent years hardware description languages have been playing an important role in the synthesis of hardware. The VLSI technology with which modern digital systems are designed has advanced at such a tremendous pace within the past few years that the engineer is being outstripped of his ability to design complex state-ofthe-art systems. Initially, various CAD tools (circuit analysis, logic minimization, layout, etc.) where made available to aid the designer in concurring such increasingly more difficult design tasks. Technology has reached a level, however, that calls for the realization of design automation system in which high-level synthesis is integrated with logic synthesis. **DIADES** design automation system which starts the synthesis process from a language called **ADL** (Algorthmic Description Language) has been developed at PSU in recent years. The main task of this thesis is to upgrade, modify and link the **DIADES** system so that it will become a pre-processor of an commercial **VHDL** -based synthesis/simulation environment from Mentor Graphics Corporation.

# 1.1 DIADES

The **DIADES** design automation system is a set of programs for the synthesis of digital circuits from high-level, behavioral descriptions. A digital system is described on the behavioral level in terms of variables and operations using a language called **ADL**. The behavioral description is compiled to a structural description, which is

composed of specific hardware units such as adders, buffers, and multiplexors. ADL is more like a programming language. It allows for easy description of parallel and sequential behavior of hardware. In this respect it is much closer to such specification languages as C or PASCAL. The main advantage is that it is easier to express parallelism in ADL than in standard HDL languages such as VHDL or VERILOG.

A digital system can be described at three levels, behavioral, functional, and structural. The language ADL is used for behavioral representation. ADL is a block-structured, algorithmic language developed especially for **DIADES** system. So it has some properties specific to **DIADES** design routines and methodologies. "High-level synthesis" in this thesis refers to the process of generating a digital circuit description on the structural level from a behavioral level description. The High-Level Synthesis in **DIADES** includes two stages: Data Path Synthesis and Control Unit Design. The data path unit contains the descriptions of the hardware elements needed to execute the behavioral algorithm.

The control unit controls the flow of data in the data path unit by producing register load signals, multiplexor addresses and other control signals. The control unit can be implemented as a micro-programmed unit or as a finite state machine using a PLA or another standard kind of logic.

Transformations and optimizations can be applied to the digital system description at all levels. Techniques from optimizing compilers, Boolean minimization, and Finite State machine minimization are some of the techniques that have been be applied in **DIADES**.

The goal of **DIADES** is to automate the process of digital system design. It is a powerful tool with many innovative and unique features. It can be used to design

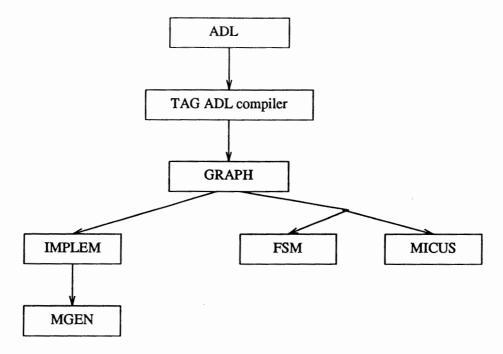

dedicated micro-controllers, digital signal processors, and other types of systems. A block diagram of the current **DIADES** system is shown in Figure 1.

Figure 1. DIADES system.

In Figure 1, TAG is the ADL compiler. GRAPH is the main intermediate format of DIADES. The data path unit is performed by IMPLEM and MGEN. IMPLEM takes the descriptions in the form of GRAPH format as an input and generates a description in an abstract netlist language called STRUCT. MGEN takes STRUCT description as input and generates a netlist in an netlist format called M language. The control unit design is created by programs FSM and MICUS. FSM is the finite state machine control unit synthesizer, it takes the descriptions in the form of GRAPH format as input and generates a truth table data format for the combinational part of the finite state machine. The MICUS is the microprogram control unit design program that takes the descriptions in the form of GRAPH format as input and generates the truth table of the control memory as its output.

#### **1.2 VHDL-BASED DIADES**

In this thesis we modify the existing DIADES system so that it will become a VHDL -based system. First the intermediate behavioral format of the DIADES's system GRAPH is converted to a VHDL code. Then the descriptions in the form of STRUCT format is converted to VHDL code. The block diagram of the new VHDL -linked DIADES system is shown in Figure 2.

All the generated VHDL code is in the Mentor Graphics VHDL format. The VHDL code generated by the VHDL -based DIADES system can be compiled by the VHDL -based mentor tools. The compiled file can be simulated or can be used for implementing it in the FPGAs. If the FPGA implementation option is chosen then the code should be synthesised and it fed to the Xilinx FPGA tools for technology maping. Then placement and routing can be done and then it can be implemented in the FPGA system. The FPGA option was given because of its almost zero turnaround time and manafacturing cost. There are also a lot of commercially available FPGAs in the market. The Xilinx FPGA is a RAM-based FPGA used by our group.

The Mentor Graphics system was selected because of its availability in the school and because of its wide range acceptance in the industry. The Mentor Graphics tools have many sophisticated Logic Synthesis, physical design, simulation or FPGA related programs that are absent from **DIADES**. **VHDL** was chosen because of its wide range and increasing use in industry. **VHDL** is a full form hardware description language. It is a very good language for detailed hardware specification. "The results (If recent industry surveys, which indicate an increased project growth in the use of

Figure 2. VHDL linked DIADES system.

VHDL, supporting the claim that VHDL is entering its deployment phase. In one survey 91% of the respondents presently not using VHDL plan to use the language in future [1]. In an informal survey the respondents projected an eightfold increase in the number of hardware designs using VHDL over the next two years [2].

The goal of this thesis is to first modify and improve the **DIADES** system and also to make it an **VHDL** -based system. The improving and modification for the

5

datapath unit of the **DIADES** system has been done in this thesis and the improvement and modification of the control unit is left for the future research.

# CHAPTER II

#### DIADES DESIGN AUTOMATION SYSTEM

#### 2.1 INTRODUCTION

The DIADES design automation system is a set of programs for the synthesis of digital circuits from high-level, behavioral descriptions [4]. The High-Level Synthesis in DIADES includes two stages: Data Path Synthesis and Control Unit Design. The data path synthesis and control unit synthesis start from a parallel program-GRAPH, the form of description that includes both the control flow and the data flow graph. While the control unit is designed to be composed of either a microprogrammed unit, or Finite State machines. The Finite State machines are minimized in two dimensions (states and inputs), assigned and realized in logic. Several logic synthesis procedures, respective to various design styles and methodologies, can be used to design combinational parts of state machines, microprogrammed units and data path logic.

The **DIADES** system uses the language **ADL** for the behavioral description of the digital system. **ADL** is a language used to describe a circuit on a high level. A circuit's behavior can be described without knowing the basic elements of the circuit, or the internal states of the controlling state machine. The description is done in terms of arithmetic and logic operations. Control flow is described using *if\_then\_else*, *go*, and *while* statements [5]. A block diagram of the current **DIADES** system is shown in Figure 3.

Figure 3. Current DIADES system.

The system is organized into four main sections. The first section takes a digital system description written in ADL and compiles it to a format called **GRAPH**. The descriptions in the **GRAPH** format represents the digital system at the behavioral level but in an easier to manipulate form. Transformations and high level optimizations such as decomposition of expressions and macro expansions take place upon the descriptions in the **GRAPH** format.

The descriptions in the **GRAPH** format is used by the data path and control unit generators. Further transformations and optimizations are applied to the digital system. Some changes in the data path are fed back into the control unit generator. The control unit generator selects one of two design styles, finite state machines and micro-programmed control units.

The fourth section takes the output of the two generator sections. This output,

which is an abstract structural form, is translated to a specific structural netlist format. Further transformations and optimizations can be applied at this level.

#### 2.2 DATA PATH SYNTHESIS

First in **DIADES** the circuit descriptions in **ADL** is converted into **GRAPH** format, which is the main intermediate format for **DIADES**. After the descriptive format has been converted to **GRAPH** format the operations in the **GRAPH** format are scheduled for execution in specific control steps. The scheduling tool in **DIADES** tries to make the best use of resources, and to increase the concurrency of the descriptions in **GRAPH** format. The descriptions in **GRAPH** format is analyzed and the order of execution of operations in it is determined. Those operations that can be executed at the same time are identified. The scheduler looks for the best sequence of operations, resulting in the shortest overall control program. After scheduling, **DIADES** assigns variables to registers and operations to specific functional units.

After allocation, the design process splits into two separate processes. The data path unit is generated by the program IMPLEM and then by the program MGEN. The DIADES data path generator, IMPLEM, takes the descriptions in the form of GRAPH format as the input. The descriptions in the GRAPH format is mapped to a hardware structure in the abstract netlist language STRUCT. The functional units, registers, and input/output ports are represented by nodes, while the connections are represented by arrows. The STRUCT description is detailized by the program MGEN, which means that abstract descriptions of structural blocks are replaced with lower level descriptions of blocks and their connections. The output format is in

netlist format called M language. For instance, the STRUCT description specifies the "abstract block" BLOCK1 - COUNTER modulo 5 with loading input A, and clock CL. The equivalent M language description will specify all flip-flops and NAND gates of this counter and how they are connected, with an accuracy to each wire and gate input.

#### 2.3 CONTROL UNIT SYNTHESIS

Two design styles are used in **DIADES** to design the control unit: the Microprogrammed Units and the Finite State Machines (FSMs). Both of them are designed starting from the descriptions in the **GRAPH** format, the main internal data representation language in **DIADES**. The result of the microprogram control unit generation is the microcode for control memory. The result of **FSM** control unit generation is the truth table or the Eqn (a set of Boolean equations) data formats for the combinational part of the FSM. The FSM synthesizer is composed of two stages, the FSM generation stage and FSM optimization stage. The first stage is a process to analyze the control flow GRAPH and assign machine states to the specified operations. It also encodes the input and the output signals for FSM structure between the control unit and the data path from different variants of the design scheme. The FSM optimization is composed of the state minimization program and the state assignment program. The state minimization reduces both the number of rows and the number of colums of state table, which is a unique feature of **DIADES**. The state assignment program encodes machine states to simplify the hardware implementation of the FSM.

The microprogrammed unit synthesizer, MICUS, first generates the SIMC (symbolic intermediate microcode) language description. Microinstruction compaction and optimization are necessary for efficient microcode. To translate SIMC further into object microcode a microassembler is used. Ultimately, a TT formatted truth table of control memory for logic minimization is generated. The optimization of the microcode is not performed separately in the control unit synthesis system, but is incorporated in the comprehensive process of data path scheduling and allocation and control unit design [6],[7].

The **DIADES** system is available in the PSU Sun network system. It is in the directory */stash/polo/newstuff/diades*. The **DIADES** system is made up of several programs written in Lisp, C, and Fortran. These programs are in a hierarchical directory structure in directory of */stash/polo*. **DIADES** is controlled by an interactive shell script called diades in the */stash/polo/newstuff/diades* directory. Each program can be executed seperately or the whole system can be executed automatically. When the shell script is executed, the user is presented a menu showing all commands and the **DIADES** framework.

#### CHAPTER III

#### ADL HARDWARE DESCRIPTION LANGUAGE

# **3.1 INTRODUCTION**

ADL is an algorithmic language devoted mainly to describe the behavior of a digital system [8],[9]. An ADL program implements some algorithm. An algorithm is a step by step procedure for solving a problem or accomplishing some task. The procedure is organized into a behavioral series of assignment statements and control flow statments. ADL also describes systems at a *functional* level or *structural* level. Systems can be formulated using a mixed description on all three levels.

An ADL program is specified by a set of input and output ports, internal or intermediate variables, and the algorithm.

ADL Program: (( Input Ports

Output Ports

Internal Variables)

( Algorithm ))

The algorithmic description is what sets this system apart from a functional level system. An ADL algorithm is similar to an algorithm in a programming language. The syntax is different but the semantics is quite close. The main difference is that a program algorithm is executed on a general purpose computer. The **DIADES** system generates a hardware processor executing only that specific algorithm.

Example 3.1.1 - An ADL program.

The header sections have been left out. The exact syntax is explained later. The program represents a simple system which adds two numbers and outputs the sum. If the result is equal to 10, the second number is subtracted from the first and the minuend is send to the output. This task is continuously repeated.

Input variables: operand1, operand2 - 8 bit numbers. Output variables: answer - 8 bit number Internal variable: temp - holds answer line 1: (((adl an example circuit .... line 2: (input (op1 (p k1 8)) (op2 (p k1 8))) line 3: (intern (temp (p kl 8))) line 4: (output (answer (p k1 8))) line 5: ((start) a line 6: 10 (temp := (op1 + op2))line 7: (if (temp = 10) then (temp := (op1 - op2)))line 8: (answer := temp)

line 9: (go 10)

line 10: )))

line 11: end

This system requires 3 clock cycles to operate. Statements are explained below:

Line 1 declares that this is a description in **ADL** language and the system name is "example circuit". The single letter "a" is a unique identifying symbol for the algorithm. Subroutines, if any, have different identifying symbols.

Lines 2 through 4 are the declarations. The declarations are similar to variable declarations in other languages. The only difference is that the functionality of

variables is defined at the start and does not change later in the program, i.e., input variables are used only for input.

Line 5 controls the start of the task. This statement is always executed when the system is powered up. However, this statement does not do anything and it is only used to initiate the operation of the control unit.

Line 6 is the first statement executed. It has the label "10". Labels are always numbers. This is a simple arithmetic operation of addition. The result of the addition is stored in variable *temp*.

Line 7 is a conditional statement. If the relation is true, then statements after the "then" keyword are executed. If the relation is false, then the next statement is executed at line 7. The value in *temp* is compared with the value 10. If they are equal, then the subtraction is performed and the value stored in *temp*. There is no "else" keyword in this statement, although they are legal.

Line 8 is a simple assignment statement. The value *temp* is stored in the variable answer.

Line 9 is a go statement. This is the simplest control flow statement. The system will go back up to the statement in line 5 and execute the task again. New data is assumed to be at the input.

Lines 10 and 11 mark the end of this simple program. More complicated programs may have other lists and program instructions before the last right parenthesis. The "end" keyword is always at the very end of all programs.

As it can be seen, the syntax of the ADL has many parentheses and reminds that of Lisp. This is because ADL is an experimental language and we want to make it easily expandable.

#### **3.2 PROGRAM STRUCTURE**

The ADL language describing a digital system has four sections. The first section contains a few lines of parameters for the ADL compiler. The second section lists variables used in the program. Variables represent the inputs and outputs of a system as well as internal registers or memories. The third section contains the algorithm. The fourth section contains any subroutine descriptions.

The simple ADL program is first broken down into 2 lists. A declaration list and an algorithm list.

```

(( (Declarations)

(Algorithm)

```

))

The declaration list is composed of several lists.

```

( program name

( Input variables )

( Internal variables )

( Output variables )

.

.

( Other Declarations )

```

The algorithm section is composed of statements. Each statement is a list.

```

((statement 1)

```

```

(statement 2)

.

.

(statement n)

```

# 3.3 Declarations

Formal grammar of declarations

Declarations ::= ( adl <symbol> <program name>

<clock list> <input variable list> <internal variable list> <output variable list> <subroutine list> <constant list> <identity list> <symb list>

<clock list> ::= (( clock (<natural number>) ));

);

<input variable list> ::= ( input <variable declaration>+ /

empty);

<internal variable list> ::= ( intern <variable declaration>+ /

empty);

<variable declaration> ::= ( <description> (<type>) ); <description> ::== <name> / <indexed variable> ; <indexed variable> ::= ( <name> [ <size> ] ); <size> ::= <natural number> / <index variable> ; <type> ::= / <d variable> ; ::= ( p k1 <number of bits> ) ; <number of bits> ::= <positive integer> ; <d variable> ::= ( d ) ;

```

<subroutine list> ::= ( subr <subroutine element>+ / empty )

<subroutine element> ::= ( <subroutine type> <symbol> <name>

( <fix flag> <parameter>+ ));

```

<subroutine type> ::= macro | block | logmacro | logblock ;

<fix flag> ::= fix / empty ;

<parameter> ::= <number> | <vector> | <parameter name> ;

<parameter name> ::= <name> ;

```

<constant list> ::= ( const <list of parameters> / empty );

```

<identity list> ::= ( iden <identity>\* / empty );

<identity> ::= ( <name> <expression> );

<name> ::= Any combination of letters and numbers ;

<expression> := <constant> | <variable> | <arithmetic expression>

/ <logical expression> / <predicate>

/ <expression> @ <expression> ;

#### **3.4 VARIABLES**

Variables in ADL are used to store data. There are 3 variable functions, input, output and internal. Input variables are used to input data to the system. Internal variables store data inside the system. Output variables are used to output data from the system. When the system is finally realized, variables are mapped to registers or memory. Because the **DIADES** system optimizes the final system's hardware there is not necessarily a one-to-one mapping of variables to registers.

There are two types of variable data. Parallel variables are vectors of binary ordered bits. Values of parallel variables are non-negative integers. Two's complement negation is done automatically in a statement by placing a minus sign in front of a variable. These are generally used for numbers or data. Logical variables are single bit variables and have two states, 1 and 0. These are usually used for flags and signals.

Example 3.4.1 - Parallel and Logical Variables.

"a" and "b" are declared as parallel variables. "c" is declared as a logical variable. To the right is a physical implementation.

> (intern (a (p k1 8)) (b (p k1 8)) (c (d)) )

$$l (b:=(and a b))$$

$$2 \qquad (b:=(and a c))$$

in statement 1, data from "a" and "b" is ANDed in parallel and stored in "b". In statement 2, the single bit from "c" is projected onto "a" and stored in "b".

Each variable can be treated as an array of bits. The array of bits is called a bit field. 1 bit binary values can be stored to or accessed from individual positions in a variable. 1 bit binary values consist of 1s and 0s. True and false symbols are not available but can be declared as constant 1s and 0s.

A range of bits in a variable can also be accessed. A range of bits is treated as a decimal number. The maximum value of a range of bits is:

2<sup>(length of range)</sup>

Example 3.4.2 - Bit Fields and Ranges in Variables

(intern (a (p k1 8))) - 8 bit variable, values range from 0 to 255.

(*a* [ 0 % 0 ]) - 1st bit in a.

(a [ 2 % 3 ]) - bits 2 and 3 of a.

(intern (b (p k1 16))) - 16 bit variable, values range from 0 to 65535.

(*b* [ 14 % 14 ]) - 14th bit in b.

Array variables are arrays of simple variables. Array variables can only be internal types.

Example 3.4.3 - ADL arrays

```

(intern ((a [256]) (p ram 32))

(b (p k1 32)))

.

.

((a [34]) := 8)

(b := (a [34]))

((a [b]) := 10)

```

An indexed array variable has the following format for internal variables:

a) (( <name> [ <size> ]) ( p <code> <bits> ))

This form is for array variables with the elements being parallel data.

```

OR

```

```

b) (( <name> [ <size> ]) ( d ))

```

This form is for array variables with the elements being logical data. The code specification has a different meaning in array variable declarations. The **DIADES** user can specify how the array is to be implemented. There are two ways;

ram - Random Access Memory

k1 - register file

If the RAM option is selected, the array will be implemented as a standard RAM element with memory size and word size as specified. The user doesn't need to be concerned with any details such as addressing and read/write signals.

If the k1 option is selected, the array is implemented as an array of individual registers. Each register can be accessed independently of the others. This option results in a much larger area needed for the array variable.

### Example 3.4.4 - Variable declarations

(a (p k1 32)) - 32 bit binary variable with name "a".

(b (p k1 6)) - 6 bit binary variable with name "b".

(c (d)) - single bit logical variable with name "c".

((d [32]) (p ram 8)) - array with 32 words. Each word is 8 bits.

Variable names start with a letter and can be any combination of letters and numbers. The length of the name is unlimited. In the main program, input variables are always implemented as input ports. They are always simple variables. They can not be assigned values from within the system and new values are determined from outside the system. These values can change at any moment of time. However the input ports are implemented as clocked buffers so new data is available each cycle.

Input variables in subroutines receive data from the main program. Depending on the subroutine type, the variables are implemented as registers or refer to variables in the main program. Internal variables contain values inside of the program, (or digital system). Data can be assigned to or retrieved, from these variables. Indexed variables are one dimensional arrays of simple variables. Normally these are specified as RAM in an ADL program. When the system is realized, internal variables may be mapped to registers or may not exist at all.

Example 3.4.5 - ADL Variables:

...

Output variables are used to output the data from the system. Unless an output variable is also declared as an intern variable, data cannot be retrieved from it. Depending on how the program is written, an output variable can either be a register or wired connection to some system element. If feedback into the system from an output variable is required, the variable is declared in both the intern and output declaration lists. The name, type and size are identical.

Example 3.4.6 - ADL output

(a := (b [k]))

(intern (a (p k1 32))) (*output* (*b* (*p* k1 32))) • (b := a)

Example 3.4.7 - Intern and Output Variables

This example shows how output variables are also declared internal, so the data from the output is also available to the system.

(intern (a (p kl 16)) (b (p kl 16)) ) (output (c (p kl 8)) (b (p kl 16)) )

$$(b := 5)$$

$(c := b)$

.

# **3.5 CONSTANTS**

Any number in ADL can be given a name. Once a constant is declared, the name can be used in any expression where the number can be used. Numbers in ADL are decimal only. A constant can be either a number or an array of numbers. If an array constant is declared, all array elements must be given values. The format for constant declarations is:

( const <constant elements>+ )

<constant elements> ::= ( <name> <number> )

Example 3.5.1 - ADL Constants:

(const (coeff\_1 42)

(coeff\_2 9))

# **3.6 IDENTITIES**

An identity is a symbol or name identical to some value, variable, or expression. Different names for the same variable can be used in ADL. Identities are declared in the identity list.

Example 3.6.1 - Identities

In this example "a" and "b" are declared identical. "e" and the range of bits 1 through 4 in array d are identical.

(iden (a b) (e (d [1 % 4])))

Identities can be declared for expressions. By using an identity for an expression, the same complicated expressions and fields of bits do not have to be repeatedly typed. Expressions are written in the same format as in the main program. Variables referred to in expressions are declared normally. The identity name itself doesn't need to be declared anywhere else. To avoid error and confusion, an identity name should not be used as variable names or a program name.

Example 3.6.2 - Identities and Expressions

In this example "id1" is declared to be identical to the expression - (or (x [ 1 % 1 ]) a):

(iden (id1 (or (x [ 1 % 1 ]) a)))

The **DIADES** system replaces identities by their corresponding values or expression during compilation of the **ADL** program. The identity list is similar to #define statements in C.

#### 3.7 SYMB LIST

A single statement can be given a symbolic name in ADL. The symbolic name can be used in place of the statement in the program. Use of symbolic names reduces the amount of repetitive typing in some programs. In the IDEN list only a single name was used to represented the identity. In the SYMB list, a whole expression or statement can be used for the symbol. Symbolic names and their statements are declared in the SYMB list.

The structure of the **SYMB** list is similar to the structure of the **IDEN** list. Symbolic names should not be used as variable names or program names. A symbolic name does not have to be a single element. It can be a combination of elements. This means whole statements can be replaced automatically with other statements. Variables in the statement are declared normally.

Example 3.7.1 - Symbolic List

$$(symb (c1 (k := (k + 1)))$$

$((a := (c + b)) (adder1 (a c b)))))$

In the first example, the c1 symbol would be replaced by the statement (k := (k + 1)) in the program. In the second example, the statement (a := (c + b)) is replaced by the subroutine call (adder1 (a c b)). The subroutine could be a structural description of a special adder.

#### **3.8 SUBROUTINES**

Subroutines can be used in ADL. The subroutine itself is listed at the end of the ADL program. Subroutine names and parameters are listed in the declarations

section. There are two types of subroutines, macros and blocks. A subroutine can be structural or behavioral. Macros and blocks can be behavioral. A logmacro subroutine is a special form of the macro and describes structure only. A macro is a sequence of statements which is represented by a single macro call statement in the main program. Macros share the same resources with the main program. A block is a separate system. **DIADES** generates a separate data path and control unit for the block.

Each subroutine is declared using the subroutine definition list. A subroutine is defined by its type, symbol, name, fix flag, and a list of parameters. The symbol, which is the same type of parameter appearing at the beginning of the main declaration block, must be unique to each subroutine and cannot be the same as any other symbols in the program. The fix flag protects the subroutine against any transformations. Transformations optimize the program in various ways. If for some reason, the user doesn't want the subroutine to be modified, the fix flag is enabled.

The parameter list is used to indicate how data is passed between the subroutine and the main program. Constants and fixed numbers can be passed to subroutines and are declared here. ADL differs from Pascal-type languages in this respect. The data direction of a variable is specified in the subroutine listing, not here in the main declaration section.

Variable parameter names can be a legal name and correspond to variable names in the subroutine listing. The positions of variables and other parameters must correspond with the positions in the subroutine listing.

Example 3.8.1 - Subroutine Declarations

(subr (macro b example macro (a b))

(block c example\_block (4 a b c)))

### 3.9 STATEMENTS AND EXPRESSIONS

## 3.9.A Introduction

ADL is a procedural language. Each statement is executed sequentially, except in parallel constructs. **DIADES** generates a machine from the program. The machine begins execution with the first statement in the program. Unless there is a loop, the last statement in the program is executed last and the machine stops. Each statement is assumed to execute in one clock cycle and is considered one operation. **DIADES** makes allowances for those statements taking more than one cycle to execute.

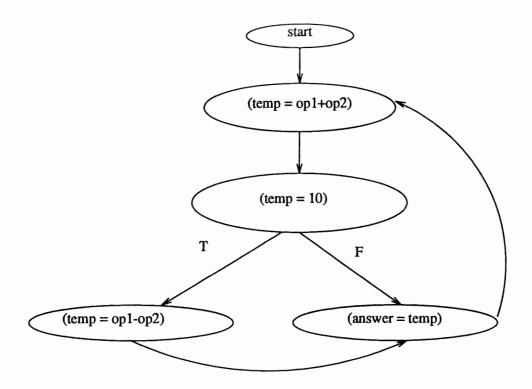

Control flow graphs are used in several examples to illustrate program fragments. Each node of a graph corresponds to a one cycle operation. Each edge corresponds to the flow of control through the graph. The following example presents the ADL program from the introduction. Following it is the corresponding control-flow graph.

Example 3.9.A.1 - Program and Flow graph

line 1: (((adl a example circuit ....

| line 2:      | (input (op1 (p k1 8)) (op2 (p k1 8)))       |

|--------------|---------------------------------------------|

| line 3:      | (intern (temp (p k1 8)))                    |

| line 4:      | (output (answer (p k1 8)))                  |

| line 5:      | ((start) a                                  |

| line 6:      | 10 (temp := (op1 + op2))                    |

| liine 7:     | (if (temp = 10) then (temp := (op1 - op2))) |

| line 8:      | (answer := temp)                            |

| line 9:      | (go 10)                                     |

| line 10: ))) |                                             |

| line 11: end |                                             |

|              |                                             |

Flow graph of the above example is shown in Figure 4.

Numbers in ADL are specified as integers or as a vector of bits. Negative integers are allowed but the form is slightly different than in other high level languages. The maximum size of an integer is limited to the size of the variable being used. Otherwise, there is no theoretical limit to the maximum integer size. Negative integers require a sub-expression using a "-" sign and a positive integer contained in a set of parentheses. For instance, -5 is written as (- 5).

Binary numbers are allowed in ADL and are referred to as vectors of bits. There is a special form for the specification of bits. The format is shown below:

```

(vect (1's and 0's))

```

Figure 4. Flow graph of example 3.9.A.1.

The bits are specified as 1's or 0's, each bit separated by a space. The most significant bit is leftmost. Leading 0's are not needed. The maximum size is limited to the size of the variable being used.

There are 3 types of statements; *assignment, conditional-control flow,* and *system control. Assignment statements* include simple variable assignments, arithmetic, and logical statements. *conditional-control flow* statements consist of go, if-then-else, while, and cond statements. *System control* statements control parallelism, process control, and starting and stopping the machine.

The basic grammar for a statement is:

<statement> ::= <label> <statement>

Each statement is contained within a set of parentheses. Most statements imply their structure but the parentheses are needed to exactly define the limits of statements. Expressions within statements also need parentheses for definition. Each level of expression requires two parentheses. Constants, numbers, and variables do not require parentheses.

Example 3.9.A.1 - Example Statements

$$(l := (l + 1))$$

$$(a := (and l a))$$

$$(if (a = 0) then (l := 4) else (l := 1))$$

$$(b := (a + (b + c)))$$

$$(while (b < 4) do (e := 0)$$

$$(b := b - 1))$$

3.9.B Labels

Statements can have **labels**. Labels are used to mark the destinations of "go" statements. "go" statements are similar to "goto" statements in BASIC. A **label** is always a number and letters are not permitted. A **label** is placed on the same line as the statement it refers to but outside the parentheses for that statement. A **label** is inside of any parentheses surrounding a block of statements. Each labelled statements must have a different **label** number.

Example - Statements with Labels

$$\begin{array}{ll} 10 & (a:=5) \\ 20 & (if (a < 5) then (a:=(a+1))) \\ & (go \ 20) \\ else \ (a:=100) \\ & (go \ 30) \\ ) \\ 30 & (c:=5) \end{array}$$

### 3.9.C Assignment Statements

The most basic statement is the assignment statement. An assignment means the transfer of the value of an expression to a variable. An expression can be a number, constant, variable, or other operation. The user can split data from one variable into two parts and two variables with an assignment statement. This is referred to as data path splitting. Two variables can be combined into one vector of bits and the new value transferred to another variable. When a program is implemented in hardware, the assignment means the loading of a register with data.

The basic grammar for assignment statements:

<assignment statement> ::= ( <left hand side>

<assignment operator>

<expression>);

<left hand side> ::= <variable> / <concatenation of variables> ; <concatenation of variables> ::= ( <variable> @ <variable> );

$\langle assignment \ operator \rangle ::= == | := | := | :=;$

<expression> := <constant> | <variable> | <arithmetic expression> | <logical expression> | <predicate> | <expression> @ <expression> ;

<predicate> ::= ( <expression>

<relation operator>

<expression> ) ;

Variables on the right hand side can not be output variables. The output of an output variable goes out of the system and is not available for transfers within the system. However, by also declaring an output variable as an intern variable, data from the output variable can be transferred within the system.

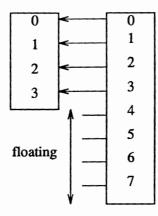

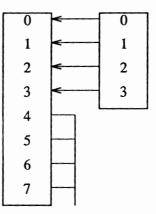

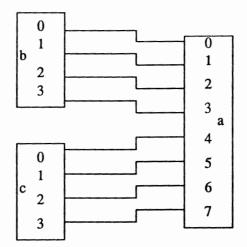

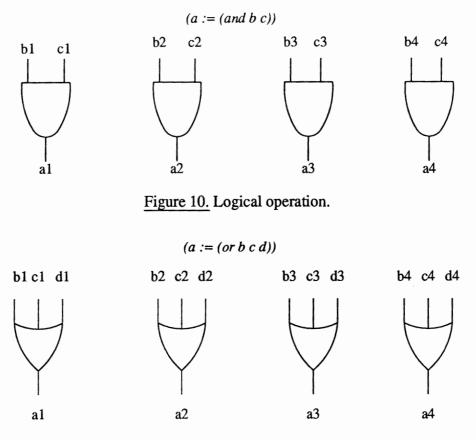

The left and right hand statements do not have to represent vectors of bits with the same size. It is possible to transfer values between variables with different sizes. If the right hand side has more bits than the left hand side, the right hand side is truncated to the correct size by dropping the extra leftmost bits from the connection between the two blocks, (Figure 5.). If the left hand side is bigger than the right hand side, extra 0 bits are added to the right hand side. These extra bits are the "most significant bits" and are added to the left side. Bits are added until the length of the right hand side matches the length of the left hand side, (Figure 6.).

Figure 5. Transfer of values between variables.

Figure 6. Transfer of values between variables.

Truncation of a variable changes the value of the destination while adding extra bits does not. The user should avoid these problems by using concatenation operations where possible.

Concatenation is a way to combine data moved between variables and expressions. Concatenation in ADL has two meanings. One meaning is the combining of two data paths into one data path. The merged data path is input to some hardware element. The other meaning is the splitting of one data path into two data paths. The two data paths are input to different hardware elements. The format for the two meanings of the concatenation symbol is identical.

The concatenation operator for ADL is the '@' symbol. The format for concatenation is as follows:

The result of the concatenation can be treated as a variable for assignments and expressions. The output from a concatenation is always input to some element or pair of elements. It can either be a lhs(lefthand), or rhs(righthand).

Example 3.9.C.1 - Concatenation

$$(A := (B @ C))$$

"A" is an 8 bit variable, B and C are 4 bit variables. The hardware implementation of this operation is to combine the outputs of the B and C registers and transfer the values into the a register, (Figure 7.). B provides the 4 low order bits and C provides the 4 high order bits into A. Example 3.9.C.2. - Data Path Splitting

Figure 7. Concatenation operation.

((B @ C) := A)

A, B, and C are variables as above. The hardware representation of this operation is to split the output of register A into the B and C registers, (Figure 8.). B takes the 4 low order bits from A and C takes the 4 high order bits.

Figure 8. Concatenation operation.

Specific fields of bits can be used with concatenation operations. This allows greater flexibility in controlling the flow of data. If the sizes do not match, then the standard defaults apply. However, the user should be careful to avoid these situations and the system will give a warning.

Example 3.9.C.3.- Concatenation with Bit Fields

((A [3 % 8]) := ((B [2 % 3]) @ (C [0 % 3])))

Figure 9. Concatenation with bit fields.

A, B, and C are variables. The hardware representation of this operation is to transfer the specified bits from the B and C registers to the A register, (Figure 9.).

#### 3.9.D Arithmetic Statements

Arithmetic statements in ADL are composed of an assignment statement and an arithmetic expression. An expression is composed of operators and operands. Operands can be expressions, variables, constants, and numbers. Arithmetic operations use an infix notation. Multi-level expressions are allowed. The order of evaluation for an expression is controlled by the parentheses.

Data in ADL are always unsigned integers. Two's complement interpretation is up to the user. The high order bit is not reserved for a sign bit. If the result of an operation is negative, the result is in two's complement form. For example, if d is a 4 bit variable with the following assignment:

$$(d := (3 - 5))$$

then:

$$(d = 14) \to true$$

also with the use of a negation operator:

$(d = (-2)) \rightarrow true$

The maximum value of an integer depends on the number of bits in the variable.

The grammar for arithmetic expressions:

<arithmetic statement> ::= ( <left hand side>

<assignment operator>

<arithmetic expression> );

<left hand side> ::= <variable> / <concatenation of variables> ;

<concatenation of variables> ::= ( <variable> @ <variable> );

<assignment operator> ::= == / := / =: ;

<arithmetic expression> ::= ( <expression>

<arithmetic operator>

<expression>);

<expression> := <constant> / <variable> / ( - <variable> )

/ <arithmetic expression>

/ <logical expression> / <relation>

/ <expression> @ <expression> ;

<arithmetic operator> := + / -;

Example 3.9.D.1 - Arithmetic expressions

(a - c) (a + (-b)) ((a + 1) - (x / y)) (((-x) + ((a \* (-c)) - b))) (b + 3) ((5 \* 6) + (a - 3))

In the above example, only arithmetic operators are used. Although the grammar for expressions is extensive, the only other operators allowed in arithmetic statements are logical operators and concatenation.

Example 3.9.D.2 - Complex Arithmetic Expressions

((a + 1) - (and x y (r @ u)))((or a b c) + (and (x + y) b))

There is no type checking in **DIADES**. Source operands and destination variables can be different sizes, creating some problems. Two 32 bit operands can be added and stored to an 8 bit operand. Only the lower 8 bits of the result will be saved and the upper 24 bits lost. **DIADES** automatically adds an overflow bit to the result of any addition or subtraction operations. Thus, the addition of two 8 bit operands results in a 9 bit result.

Subtraction operation converts the subtrahend into a two's complement representation and adds it to the minuend. If the result is negative, the result will be a two's complement number. If the subtrahend is the result of another subtraction operation and is negative, it is still converted into a two's complement and added to the minuend.

Multiplication and division operations are included in ADL even though they are not implemented in the **DIADES** system. There are no corresponding hardware elements for multiplication and division so these two operations cannot be used.

The size of the result of an arithmetic operation is always equal to the size of the largest operand. Problems can arise when two large numbers are used and the result is too large for the destination.

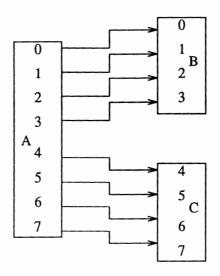

#### 3.9.E Logical Operations

Logical statements in ADL are composed of an assignment statement and a logical expression. A logical expression takes any number of operands and maps them onto a logical operator. Any expression can be an operand. The number of operands is unlimited except for "exor" which takes two operands and "not" which takes one operand. Logical expressions use a prefix notation.

#### Example 3.9.E.1 - Logical Operation

If all the operands of an expression have one bit, the result of the logical operator is one bit. If the operands have different sizes, the result of the logical operator is equal to the size of the largest operator. Smaller operands have 0s added to the more

Figure 11. Logical operation.

significant sides.

There are two types of variables in ADL, "d" and "p" types. The "d" type is a logical variable and is not used for numbers. It is always one bit. The "p" type is an array of bits and can be used for numbers. The important difference between them is their interpretation in logical expressions. "p" type operands are mapped onto the logical operator. The operator is applied to each set of bits from the operands. "d" type operands have one bit. If the other operands are "p" type, the "d" bit is projected onto the bits of the other operands and the logical operator is applied.

Example 3.9.E.2 - Logical Expressions

In this example:

"p" type:

$$a = 0111 = 3$$

$$b = 0110 = 6$$

$$c = 011101 = 29$$

$$d = 10 = 2$$

$$e = 1 = 1$$

"d" type:

$$f = 0$$

$$g = 1$$

(not a) = 1000

(and a b) = 0110

(or c d) = 011111

(and e d) = 00

(and e f) = 0

(nor (a + b) c) = 000010

(and (a + b) (c - d)) = 001001

The grammar for logical statements:

<logical statement> ::= ( <left hand side>

<assignment operator>

<arithmetic expression> );

<left hand side> ::= <variable> / <concatenation of variables> ;<concatenation of variables> ::= ( <variable> @ <variable> ) ;

<*assignment operator*> ::= == / := / =: ;

### 3.10 CONTROL FLOW STATEMENTS

Control flow statements are used to control execution of branches in the program. Go statements branch unconditionally.

**If-then-else** and **while-do** statements allow the program to have several branches. The branch executed depends on the value of the predicate in the control statement. **Cond** statements select one of several branches depending on the value of a predicate at the beginning of each branch. **Wait** statements hold the system in a loop for a specific time or until some input value changes.

The basic grammar of control flow statements is:

<control flow statement> ::= <go statement> /

<if then else statement> / <while statement> / <cond statement> /

#### <wait statement>;

Each statement, except go, uses a predicate to control branching. Predicates are expressions which have two values, true and false. True is represented by one bit with value 1 and false by one bit with value 0. A predicate consists of one or more relations linked with a logical connective such as "and" or "or". A relation consists of a relational operator and two operands. An operand can be a number, constant, variable, or expression. The basic grammar for a predicate is:

```

<predicate> ::= ( <expression>

```

<relational operator> <expression> ) or ( <expression> ) ;

<*relational operator*> := = / < / > / ;

Example 3.10.1 - Predicates

$$a = 3 \ b = 1 \ c = 2$$

(  $a = 3$  ) -> true

(  $a = b$  ) -> false

(  $a > 7$  ) -> false

$$(b < 8)$$

-> true

$(a = (b + c))$  -> true

$((5 - a) > (c + 4))$  -> false

$(and (a = 3) (b < 8))$  -> true

$(or (a = b) (a > 7))$  -> false

$(not (b < 8))$  -> false

$(nor (a = (b + c)) (b = 1))$  -> false

### 3.10.A Go Statements

Go statements are used to unconditionally branch to a labelled statement. Go statements and their corresponding destination statements can occur anywhere in the program. Jumps out of if-then else statements and while loops are allowed. Although it is not a good programming practice, the destination statement can be inside of a while loop. The "value" of a label cannot be created using an expression. For example: (i := 99) and (go i) is invalid. The basic grammar for the go statement is:

<go statement> ::= ( go <label> );

Example 3.10.A.1 - Program with Go Statements

(((adl a example

(input (a (p k1 8)) (b (p k1 8)) (c (p k1 8))) (intern (j (p k1 8)) (k (p k1 8)) (l (p k1 8))) (output (x (p k1 8)) (y (p k1 8)) (z (p k1 8)))

((start) a

$$10 \quad (j := (a + 1)) \\ (go 30) \\ 20 \quad (k := (a + b)) \\ (go 40) \\ 30 \quad (l := (b + c)) \\ (go 20) \\ 40 \quad (x := (j - k)) \\ (go 10) \\ ))) \\ end$$

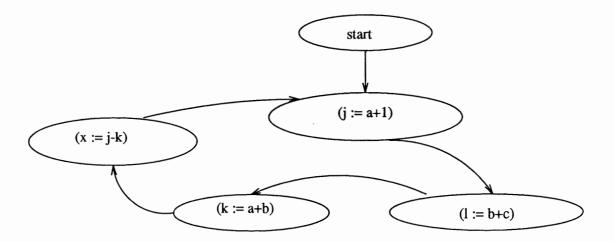

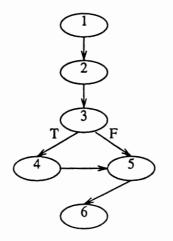

The flow graph of the above program is shown in Figure 12.

Figure 12. Flow graph for example 3.10.A.1.

# 3.10.B If-Then-Else Statements

There are two forms of the conditional **if** statement: with an "else" and without an "else". The statement consists of an **"if"** keyword, followed by a predicate. The predicate is followed by a "then" keyword. If the predicate is true, the statements following it are executed. The "else" keyword follows those statements. If the predicate is false, statements following the "else" keyword are executed. If there is no "else", statements after the if-then block are executed. The basic grammar of the **if** statement is:

```

<if statement> ::= ( if <predicate> then <statement>+ ) /

```

or ( if <predicate> then <statement>+else <statement>+ );

Unlike C or Pascal, there are no explicit symbols defining the extent of the **if-then-else** statement. In Pascal, begin and end keywords mark the sequence of statements being executed. In **ADL** the "then" keyword and either the "else" keyword or right parenthesis mark the sequence of statements executed if the predicate is true. The "else" keyword and the right parenthesis mark the sequence of statements executed if the predicate is false.

Example 3.10.B.1. - Program with If Statements

```

(((adl a example

```

```

(input (a (p k1 8)) (b (p k1 8)))

(intern (j (p k1 8)) (k (p k1 8)))

(output (x (p k1 8)) (y (p k1 8)))

```

((start) a

)

```

(if (a = 3)

then

(j := (a + b))

(k := (and j (or (a + b) a)))

else

(x := 5)

)

(y := 8)

(if (k > (j + a))

then

(y := 32)

)

))))

end

```

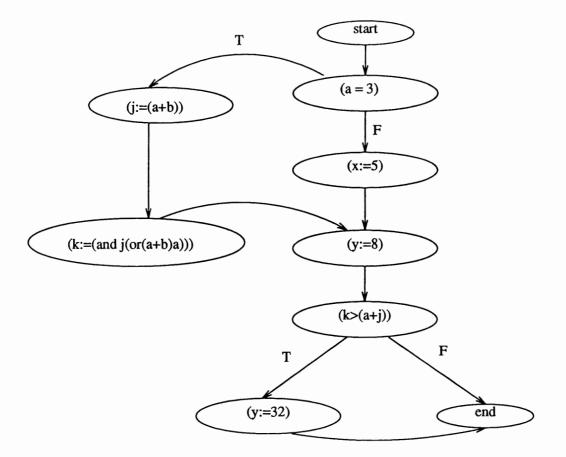

The flow graph of the above program is shown in Figure 13.

# 3.10.C While Loops

ADL supports while loops. A while statement consists of the while keyword followed by a predicate and the **do** keyword. Statements between the **do** keyword and the right parenthesis are executed repeatedly until the predicate is false. If the predicate is false before the start of the loop, the statements in the loop are not executed. The basic grammar is shown below:

<while statement> ::= ( while <predicate> do <statements>+ );

Figure 13. Flow graph for example 3.10.B.1.

Example 3.10.C.1 - Program with While Loop

(((adl a example

```

(input (a (p k1 8)) (b (p k1 8)))

(intern (j (p k1 8)) (k (p k1 8)))

(output (x (p k1 8)) (y (p k1 8)))

```

((start) a

)

( while (a = 3) do (j := (a + b)) (k := (and j (or (a + b) a))) ) (y := 8) (while (k > (j + a)) do (y := 32) )))) end

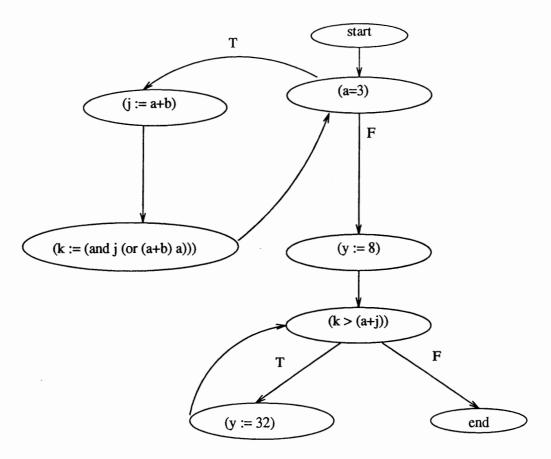

The flow graph of the above program is shown in Figure 14.

Any statements can be executed in the while loop except return, drop, and stopadl. Jumps into and out of the loop with the go statement are allowed. Nested while loops are allowed.

If the predicate variables are input variables, they do not have to be initialized. If they are **intern** variables, they should be initialized before the **while** statement is executed. The predicate is evaluated first. If true, the statements within the loop are executed and the predicate is evaluated again. If the predicate is false, execution continues with the statement following the **while** statement.

Normally, the predicate variable should change in the body of the loop so that the loop is exited. This is true for **intern** variables. It is not true for **input** variables because their values are changed from outside the system and the user cannot change those from within the program.

Figure 14.Flow graph for example 3.10.C.1.

Example 3.10.C.2 - Nested While Loops

(((adl a example

(input (a (p k1 8)) (b (p k1 8))) (intern (j (p k1 8)) (k (p k1 8))) (output (x (p k1 8)) (y (p k1 8)))

)

((start) a

(while (a = 3) do

(j := (a + b))

(k := (and j (or (a + b) a)))

(while (j > 10) do

(j := (j + 1))

(x := (nor a b c))

)))

end

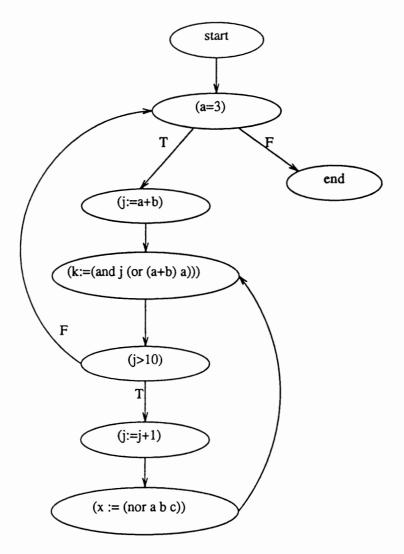

The flow graph of the above program is shown in Figure 15.

# 3.10.D Cond Statement

The cond statement is a an extension of the **if-then-else** statement. Within the cond statement can be several branches, but only one is executed. Each branch has its own predicate controlling execution of that branch. When a **cond** statement is encountered, the predicate of the first branch is executed. If it is true then that branch is executed and program execution continues with the next statement after the **cond** statement. If the first predicate is false then the next branch is executed. This process goes on until one of the branches is executed or the end of the **cond** statement is reached. There is no "default" branch. There must be at least two branches in a cond statement. Jumps out of a **cond** statement using the "go" statement are allowed. The basic grammar for the **cond** statement is presented below:

<cond statement> ::= ( cond <cond branch>+ );

<cond branch> ::= ( <predicate> <statement>+ );

Example 3.10.D.1 - Cond Statements

(((adl a example

(input (a (p k1 8)) (b (p k1 8)) (c (p k1 8))) (intern (j (p k1 8)) (k (p k1 8)) (l (p k1 8))) (output (x (p k1 8)) (y (p k1 8)) (z (p k1 8))) 52

((start) a

10

$$(cond ((b = 0) (x := 1)))$$

$((not (b = 0)) (y := 0) (z := 0)))$

$(cond ((a = 0) (go 10))$

$((a = 1) (while (j > 10) do (j := (j + 1)))$

$(x := (nor a b c)))$

$)))$

$((c = 23) (l := 1))$

$((j = 3) (x := 0) (k := (k + 2)))$

))))

end

The flow graph of the above program is shown in Figure 16.

## 3.11 SPECIAL STATEMENTS

This section describes statements which are unique to ADL. They provide more control over hardware operations. These statements include a wait statement which holds the digital system in a timing loop until some condition is met and set and reset statements which assert output values.

# 3.11.A A Wait Statements

The wait statement is used to hold the digital system in a timing loop for a fixed amount of cycles or until some external condition is met. The wait statement with a

Figure 16. Flow graph for example 3.10.D.1.

number is used to hold the system for a fixed time. The **wait while** statement with a predicate is used to hold the system until an external condition is met. Variables used in a **wait while** statement must be **input** variables because internal variables will not change during the timing loop. The **wait** statement is an extension of a **for** loop or while loop. The basic grammar for this statement is presented below:

```

<wait statement> ::= ( wait <number> ) /

```

54

( wait while <predicate> );

Example 3.11.A.1 - Wait Statements

(wait while reservoir\_full)

(wait while (and (x [ 1 % 1 ]) r ))

(wait 1000)

# 3.11.B Set and Reset Statements

Set and reset statements control the turning on and off of many one bit signals. Set means an output variable is 1 and reset means an output variable is 0. This application is common in industrial control circuits. The basic grammar is shown below:

<set and reset statements> ::= ( set <logical variable>+ ) /

( reset <logical variable>+ );

Only logical variables can be set and reset because they are one bit signals. Once a variable is set or reset, it holds that value until the variable is changed.

Example 3.11.B.1 - Set and Reset

(set a b c) (reset x y z)

### 3.11.C System Control Statements

System control statements are divided into two groups, statements controlling the starting and stopping of the digital system, and statements controlling parallel operations.

# 3.11.D Parallel Execution Statements

In **DIADES** the user can design a system with parallel operations. Parallel operations use the same control unit but multiple hardware elements are enabled at the same time. An **ADL** program can be written so that individual statements or blocks of statements operate in parallel. Multiple statements can be directed to execute in the same cycle. An algorithm can be split into parallel blocks of statements. Control statements join parallel blocks back into one process.

## 3.11.E A Multiple Statement Execution

The sim instruction is used to execute more than one assignment instruction in the same cycle. Sim stands for simultaneous execution of statements. All statements within the scope of the sim instruction are executed in the same cycle. Only assignment statements can be executed. The basic grammar for the **sim** instruction is:

<sim instruction> ::= ( sim <assignment instruction> );

Example 3.11.E.1 - Sim Instructions

In this example, x and k are incremented in parallel.

$$(sim (x := (x + 1)))$$

$(k := (k - 1))$

In this example, x is loaded with 1, a is loaded with 5, and b is anded with x and a.

(sim (x := 1) (a := 1) (b := (and x a))

At least two statements must be within the sim instruction. If the same variable appears on the left side of one assignment statement and on the right side of another in the same sim instruction, the TAG compiler will print a warning about conflicting variables. This is not an error but a warning to possible problems with this kind of instruction in the next phases of system design. An warning is also printed if the number of bits doesn't match in a field specification.

#### 3.12 PARALLEL PROGRAM EXECUTION

An algorithm is a process. Using parallel control instructions, a process can be split into two or more branches. Each branch executes in parallel with the other branches. Each branch operates independently of the other branches and communication between branches is through internal variables. When one or all branches are finished, they can be joined together into one process or just stop. A branch can stop when it is finished, wait for other branches to finish, or cause other branches to stop. Fork is the name of the branching instruction and the basic grammar is described below [10].

```

<fork instruction> ::= (fork <branch>+ <branch control> );

```

```

<branch> ::= ( <instructions> <drop control> );<br/><drop control> ::= ( drop );

```

<branch control> ::= dand | dexor ;

The fork instruction is composed of the keyword fork, followed by each branch which is enclosed in a set of parentheses. After the branches are described, the branch control parameters are described. Control parameters indicate how control passes from the branches to a single process.

There must be at least two branches in a fork instruction. Each branch is made up of almost all ADL statements, including parallel control statements. The restrictions are the following:

1. Labels can not be placed on the last statement in a branch.

2. Jumps out of, into, and within the branch are allowed. Jumps out of and into the fork statement are also allowed. However, programming like this causes problems and the user should be very careful.

3. Instructions drop, return, and stopadl cannot be the only instruction in a branch.

Branches can be joined into a single process. When one or more branches have completed execution, the overall execution process continues with the next statement after the **fork** statement. The branch control instructions indicate how this is done. The **drop** instruction individually controls each branch and appears as the last statement in a branch. **Dand** and **dexor** instructions control all branches and are normally placed in the **fork** statement after all the branch statements.

1. **drop** - When the branch is finished executing and drop instruction is reached, control is terminated in this branch. Program control is left to the other branches. If all the other branches have **drop** instructions, then

the execution of the next statement after the fork takes place when the last branch has finished. If the other branches are controlled by dand or dexor instructions and finish before the branch with the drop, the branch with the drop keeps executing in parallel with the rest of the program.

2. dand - When any of the branches is finished executing, this instruction is reached and execution of the next statement after the fork does not take place until all branches have completed execution. If a branch has a drop instruction, that branch is ignored for the scope of the dand.

3. Dexor - When any of the branches is finished executing, this instruction is reached and control passes to the next statement after the fork. All other branches stop execution immediately except for branches with drop instructions. These will continue executing until finished. There are some special cases where parallel branches continue executing after the **dexor** instruction is reached.

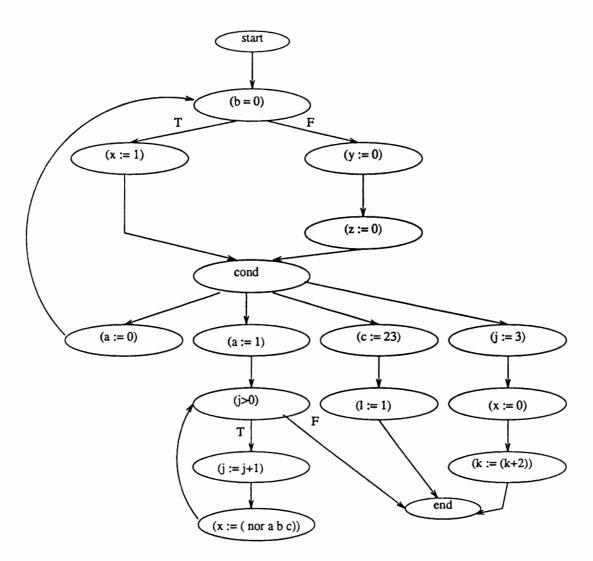

Example 3.12.1 - Fork Example

### (((adl a example382

```

(input (a (p k1 8)) (b (p k1 8)) (c (p k1 8)))

(intern (j (p kl 8)) (k (p kl 8)) (l (p kl 8)))

(output (x (p k1 8)) (y (p k1 8)) (z (p k1 8)))

((start) a

```

111 (x := 10)

)

(fork

((x := 4) (go 111)) ((y := 33) (x := (b + 34)) (drop)) ((z := (and a b)) (k := (j + e)) ((j := 45) (while (j > 23) do (j := (j - 1)))) dexor

)

)))

end

The flowgraph of the above program is shown in Figure 17. The first branch ends with the jump out of the branch and **fork** statements to some other point of the program. The second branch ends when the two assignments are completed and the **drop** instruction is reached. The third and fourth branches are controlled by the **dexor** instruction. When one of them finishes, the other branch is stopped and the program execution continues with the first statement after the fork instruction. In this particular example, it is obvious that the third branch finishes first. The variable x will have the last value calculated before the branch was stopped.

When the dexor instruction is reached within a fork statement, all other branches within the scope of the fork statement stop. The dexor instruction only affects statements inside the fork statement. If a jump is made out of the fork statement to another section of the program, that section will be executing in parallel with the branches inside of the fork statement. When one branch is finished and the dexor instruction is reached, branches within the fork statement stop but the section outside of the fork statement continues to execute.

There is a special form of the dexor instruction. If labels are placed at the

Figure 17. Flow graph for example 3.12.1.

beginning of branches, (within the parentheses), the dexor instruction only affects the control of specified branches. The **dexor** statement is placed outside of the **fork** statement as a separate labeled statement. The syntax for this is shown below:

<label> (dexor <label>+)

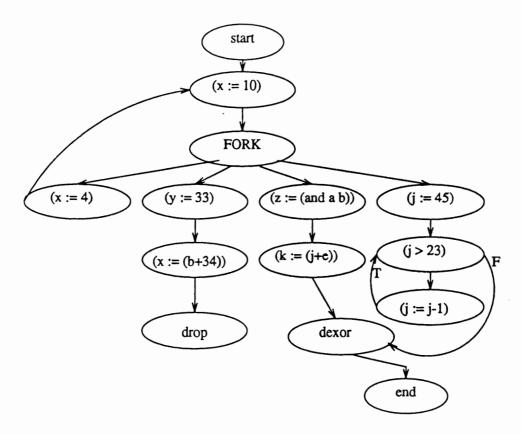

Example 3.12.2 - Fork with Dexor Specification

(((adl a example (input (a (p k1 8)) (b (p k1 8)) (c (p k1 8))) (intern (j (p k1 8)) (k (p k1 8)) (l (p k1 8))) (output (x (p k1 8)) (y (p k1 8)) (z (p k1 8)))

# )

```

((start) a

```

```

1 \quad (x := 10)

(fork

((x := 4) (y := 5) (drop))

(4 (y := 33) 5 (x := (b + 34)) (go 3))

(6 (z := (and a b)) (go 3))

((j := 45) (go 1)))

3 \quad (dexor 4 5 6 3)

)))

```

```

end

```

Tokens in nodes 4, 5, 6, and 3 are canceled if any one of them finishes and a jump is made to the **dexor** statement. All other branches started from this **fork** statement continue. The flowgraph for this example is shown in Figure 18.

### CHAPTER IV

#### **GRAPH LANGUAGE**

### **4.1 INTRODUCTION**

**GRAPH** language is a format used in **DIADES** to represent the behavior of a digital system. The behavior is represented by a specific sequence of program statements. **GRAPH** is based on a standard directed graph. It basically consists of a set of nodes and arrows. A node represents an operation or program statement. An operation can be a variable transfer, arithmetic operation, logical operation, or comparison. An arrow represents the flow of control from one node to another. For example, an arrow from node 1 to node 2 means node 1 is executed first and then node 2 is executed. Control of the digital system is transferred from node 1 to node 2. The **GRAPH** is not evaluated as a whole but a path can be traced through the **GRAPH** representing a sequence of operations.

Control can flow through the **GRAPH** in several ways. Each node is executed sequentially, following the path of the arrows. Some nodes are condition checks. The value of a variable is compared to some expression. The control flow can split into two branches. One branch is when the result of comparison is true and another is when result of the comparison is false. The execution of the branches is mutually exclusive. Only one branch will be executed at a time. Some nodes represent multiway branches. Each condition is checked until a true one is found. The corresponding branch is executed and the others skipped.

Normally only one node is executed at a time. There is a way to execute nodes simultaneously. Multiple branches can be defined and executed concurrently. The control flow splits to go in parallel through the branches. The parallel control flows can be joined together in different ways resulting in a single control flow.

The data structure for **GRAPH** is more complicated than a simple di-graph. There are several node and arrow types, each with different properties. Each property affects how the **GRAPH** description is interpreted and executed. For example, some nodes are data transfer type operations and some are condition checks. Some node properties affect how arrows are interpreted. Some arrows represent sequential execution, while others represent concurrent execution.

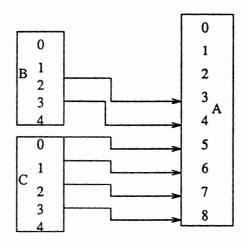

The implementation of GRAPH consists of several Lisp lists. The three main lists are the COPLISSET, the NALISSET, and the PLISSET. The COPLISSET represents arrows. The NALISSET represents nodes containing regular operations and data transfers. The PLISSET represents nodes containing comparison operations. Because it is not a pure graph implemented with pointers, all nodes are assigned numbers. Each of the lists uses these numbers to refer to nodes. Some nodes are not listed in either the NALISSET or PLISSET lists. These nodes usually are used to control execution and are described in the auxiliary lists, NOLISSET and ANLISSET. Nodes which are identical to some other node are not listed in the NALISSET list. Instead, they are listed as being equivalent to other nodes in the NOLISSET list. The other lists contain information about variables, the number of blocks, and any structural descriptions. The entire ADL description is also contained in one list for reference by some DIADES programs that use GRAPH language.

# 4.2 COPLISSET LIST

The COPLISSET list contains all the arrows in the GRAPH The arrows indicate how control flows through the GRAPH in GRAPH. Control can flow from one node to another or it can depend on the results of a comparison, (a condition check). An element consists of a symbol indicating the control transfer type, the source node number and the destination node number. These numbers reference to elements of other lists. The formal definition of a COPLISSET entry follows:

```

<COPLISSET element> ::=

```

(<control transfer type>

<source>

<destination>

);

```

<control transfer type> ::= e / x

```

/ <node number>

/ (not <node number>);

<source> ::= <node number> ;

<destination> ::= <node number> ;

The source and destination nodes can not be the same. The implementation of a conditional loop requires the use of a dummy node. Dummy nodes are described in the NOLISSET list. An x type transfer means control is transferred unconditionally from the source node to the destination node. An e type transfer means there are parallel execution paths from the source node. There will be at least one other arrow with an e transfer type from the same source node to a different destination node. If a node number is given as the transfer type, this means that node is a comparison

operation. The destination node depends on the comparison result. If the result of the comparison is true, then the control transfers to the destination node. If it is false, then the control is not transferred. If the not keyword precedes the node number and is in a sublist, then the control is transferred to the destination node if the comparison result is false. Regular condition checks require two arrows, one for true and one for false.

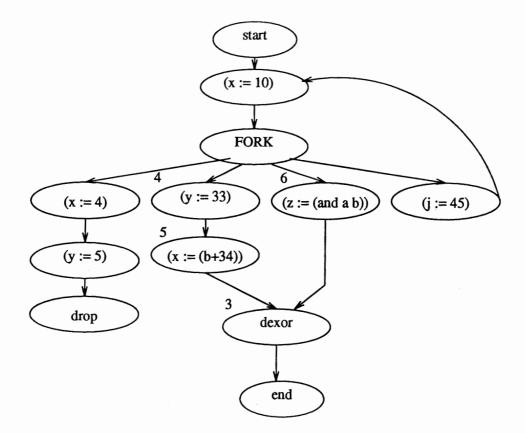

Example 4.2.1 - Conditional and Unconditional Control Transfer

(x 1 2) (x 2 3) (3 3 4) ((not 3) 3 5) (x 4 5) (x 5 6)

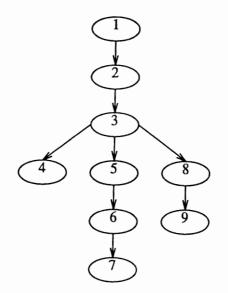

The flow graph of the above example is shown in Figure 19.

Figure 19.Flow graph for example 4.2.1.

# Example 4.2.2 - Parallel Control Transfer

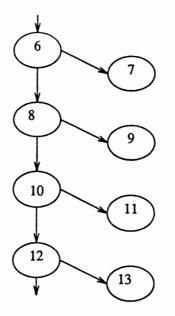

(x 1 2) (x 2 3) (e 3 4) (e 3 5) (x 5 6) (x 6 7) (e 3 8) (x 8 9)

The flow graph of the above example is shown in Figure 20.

Figure 20. Flow graph for example 4.2.2.