Portland State University PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

3-24-2020

# Extensible Performance-Aware Runtime Integrity Measurement

Brian G. Delgado Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Computer Sciences Commons Let us know how access to this document benefits you.

#### **Recommended Citation**

Delgado, Brian G., "Extensible Performance-Aware Runtime Integrity Measurement" (2020). *Dissertations and Theses.* Paper 5425. https://doi.org/10.15760/etd.7298

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

Extensible Performance-Aware Runtime Integrity Measurement

by

Brian G. Delgado

# A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

Dissertation Commitee: Karen L. Karavanic, Chair Charles V. Wright Wu-chang Feng Bruce Irvin Wayne Wakeland

Portland State University 2020

©2020 Brian G. Delgado

#### Abstract

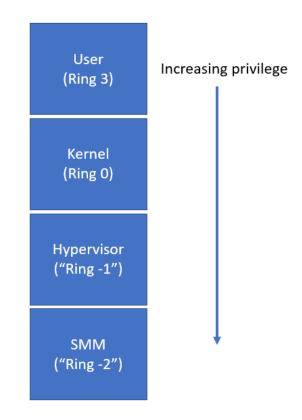

Today's interconnected world consists of a broad set of online activities including banking, shopping, managing health records, and social media while relying heavily on servers to manage extensive sets of data. However, stealthy rootkit attacks on this infrastructure have placed these servers at risk. Security researchers have proposed using an existing x86 CPU mode called System Management Mode (SMM) to search for rootkits from a hardware-protected, isolated, and privileged location. SMM has broad visibility into operating system resources including memory regions and CPU registers. However, the use of SMM for runtime integrity measurement mechanisms (SMM-RIMMs) would significantly expand the amount of CPU time spent away from operating system and hypervisor (host software) control, resulting in potentially serious system impacts. To be a candidate for production use, SMM RIMMs would need to be resilient, performant and extensible. We developed the EPA-RIMM architecture guided by the principles of extensibility, performance awareness, and effectiveness. EPA-RIMM incorporates a security check description mechanism that allows dynamic changes to the set of resources to be monitored. It minimizes system performance impacts by decomposing security checks into shorter tasks that can be independently scheduled over time. We present a performance methodology for SMM to quantify system impacts, as well as a simulator that allows for the evaluation of different methods of scheduling security inspections. Our SMM-based EPA-RIMM prototype leverages insights from the performance methodology to detect host software rootkits at reduced system impacts. EPA-RIMM demonstrates that SMM-based rootkit detection can be made performance-efficient and effective, providing a new tool for defense.

#### Acknowledgements

This dissertation would not have been possible without the support of many people. Professor Karavanic greatly helped encourage the work forward and navigate the complex intersection of performance and computer security.

I began this academic journey due to the encouragement of my former Intel manager, Jeff Demain, who encouraged me to pursue graduate studies. I also had the fortune to learn about performance measurement while working with Raed Kanjo at Intel who taught me techniques that were invaluable in this analysis. Dave Riss, Dion Rogers, and Chris Kachigian were instrumental in navigate my academic path at Intel in recent years.

The patience of my family has been helpful along the way in dealing with the long hours. My uncle, David, encouraged me on to complete the work and also gave me inspiration due to his own academic path.

I gratefully acknowledge the help of the entire EPA-RIMM team: Tejaswini Vibhute for many helpful discussions on EPA-RIMM and STM, John Fastabend for diving into multicore and coreboot, Cody Shepherd for significantly refining the software stack and many helpful questions, Dylan Abraham for leading the release process for EPA-RIMM and getting the code ready, Payal Joshi for discussions on measurement triggers and the Oracle, Alex Freed for his inputs and jumping in to test the release code, and our intern crew for finding interesting corners of this project to explore.

#### **Grant Information**:

*"This material is based upon work supported by the National Science Foundation under Grant No. 1528185.*

Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation."

## Table of Contents

| Al | ostrac      | t       |                                                       | i        |

|----|-------------|---------|-------------------------------------------------------|----------|

| A  | cknov       | vledger | ments                                                 | ii       |

| Li | st of [     | Tables  |                                                       | ix       |

| Li | st of ]     | Figures |                                                       | x        |

| Li | st of A     | Abbrev  | iations                                               | xiii     |

| Li | st of S     | Symbol  | ls                                                    | xvi      |

| 1  | Intro       | oductio | on                                                    | 1        |

|    | 1.1         | In-Sco  | pe Attacks                                            | 9        |

|    |             | 1.1.1   | 1                                                     | 10       |

|    |             |         | 1.1.1.1 IDT Hooking $\ldots$                          | 10       |

|    |             |         | 1.1.1.2 SMEP Disable                                  | 10       |

|    |             |         | 1.1.1.3 Kernel Rootkit Code Injection                 | 11       |

|    |             |         | 1.1.1.4 System Call Hooking                           | 11       |

|    |             |         | 1.1.1.5 Xen Venom Rootkit VM Escape                   | 11       |

|    |             |         | 1.1.1.6 Xen Exception Handler                         | 12       |

|    | 1.2         | Kev C   | hallenges for SMM-RIMMs                               | 13       |

|    | 1.4         | 1.2.1   | C1 - SMM-RIMM Security                                | 13       |

|    |             | 1.2.2   |                                                       | 17       |

|    |             |         | C3 - SMM-RIMM Performance                             | 17       |

|    |             | 1.2.4   | C4 - Measurement Variability                          | 18       |

|    |             | 1.2.5   | C5 - SMM-RIMM Code Availability                       | 19       |

|    | 1.3         |         | ibutions                                              | 20       |

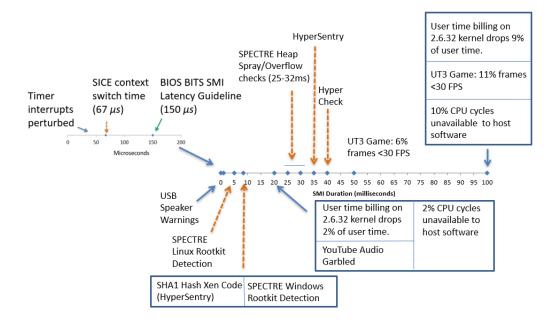

|    | 1.0         | 1.3.1   | First Linkage of SMI Latency Guidelines and Perfor-   | 20       |

|    |             | 1.0.1   | mance Impacts to SMM-RIMMs                            | 20       |

|    |             | 1.3.2   | First performance-aware SMM-RIMM design incorpo-      | 20       |

|    |             | 1.0.2   | rating measurement decomposition                      | 22       |

|    |             | 1.3.3   | First application of measurement triggers to SMM-RIMM |          |

|    |             | 1.3.4   | First SMM-RIMM Benchmark: EPA-RIMM Bench              | 23       |

|    |             | 1.3.5   | First Publicly-Available SMM-RIMM Prototype           | 23<br>24 |

|    | 1.4         |         | nent Organization                                     | 24<br>24 |

| 2  | Bacl        | cgroun  | d                                                     | 26       |

| -  | 2.1         | 0       | u<br>t Landscape                                      | 26       |

|    | 2.2         |         | Approaches for Securing Systems                       | 27       |

|    | 2.2         |         | t Need for Runtime Checking                           | 29       |

|    | 2.3<br>2.4  |         | n Impact of SMM                                       | 32       |

|    | 2.4<br>2.5  | -       | -                                                     | 32<br>34 |

|    | <b>Z.</b> J | ingge   | prs                                                   | 94       |

v

| 3 | Related Work 36 |                                                            |  |  |

|---|-----------------|------------------------------------------------------------|--|--|

|   | 3.1             | 3.1 Race to the Bottom                                     |  |  |

|   | 3.2             | Software-based Approaches                                  |  |  |

|   | 3.3             | Hardware-based Approaches                                  |  |  |

|   |                 | 3.3.1 Discrete Devices                                     |  |  |

|   |                 | 3.3.2 CPU Virtualization                                   |  |  |

|   |                 | 3.3.3 CPU Performance Counters                             |  |  |

|   |                 | 3.3.4 TPM                                                  |  |  |

|   |                 | 3.3.5 Late Launch                                          |  |  |

|   |                 | 3.3.6 ARM TrustZone                                        |  |  |

|   |                 | 3.3.7 SMM-RIMMs                                            |  |  |

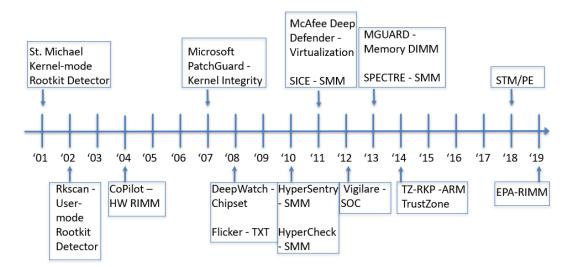

|   | 3.4             | Timeline of Approaches 51                                  |  |  |

|   | 3.5             | Application Noise                                          |  |  |

|   |                 | 11                                                         |  |  |

| 4 | Crea            | ation of Methodology for SMI Performance Measurement 54    |  |  |

|   | 4.1             | SMM-RIMM Performance Methodology Requirements 55           |  |  |

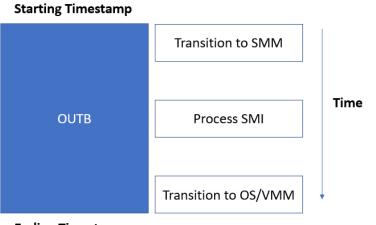

|   |                 | 4.1.1 Ability to quantify time spent in SMM - Rquantify 56 |  |  |

|   |                 | 4.1.2 Ability to control time spent in SMM - Rcontrol 59   |  |  |

|   |                 | 4.1.3 Ability to validate SMI load - Rvalidate             |  |  |

|   | 4.2             | Related Work                                               |  |  |

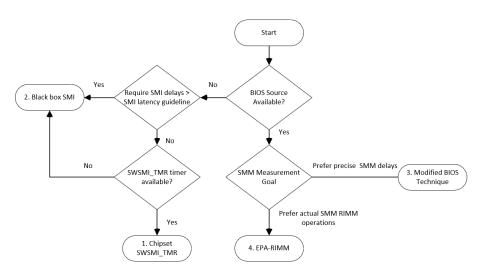

|   | 4.3             | Measurement Methodology Creation 61                        |  |  |

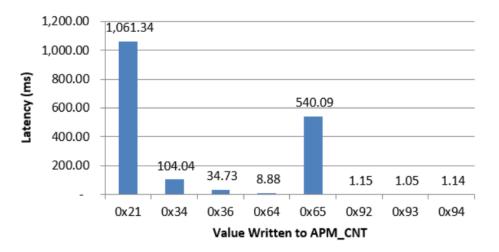

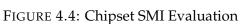

|   | 4.4             | Technique 1: Chipset SMIs    62                            |  |  |

|   | 4.5             | Technique 2: Blackbox SMI Generation                       |  |  |

|   | 4.6             | Technique 3: Modified BIOS    67                           |  |  |

|   | 4.7             | Technique 4: EPA-RIMM    67                                |  |  |

|   | 4.8             | Technique Comparison    68                                 |  |  |

|   | 4.9             | Validating the SMI Load                                    |  |  |

|   | 4.10            | SMI Generation                                             |  |  |

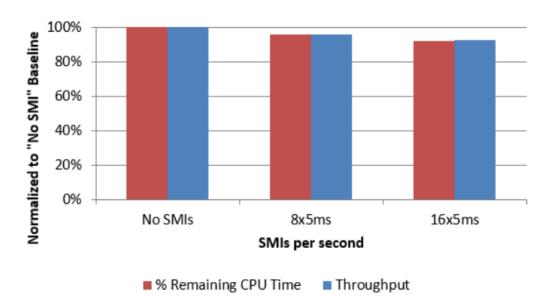

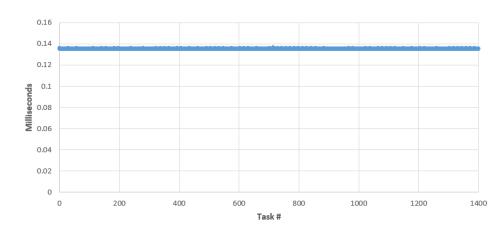

|   | 4.11            | Task Provisioning7272                                      |  |  |

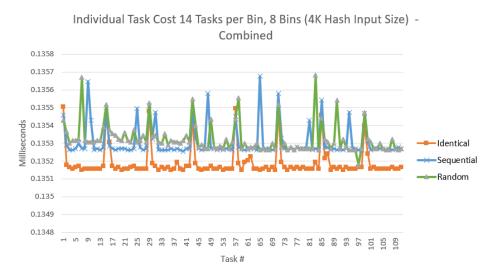

|   |                 | 4.11.1 Cache and Prefetcher Impact Measurement Study 73    |  |  |

|   |                 | 4.11.1.1 Measurement Design                                |  |  |

|   |                 | 4.11.1.2 Identical Addresses                               |  |  |

|   |                 | 4.11.1.3 Sequential Addresses                              |  |  |

|   |                 | 4.11.1.4 Random Addresses                                  |  |  |

|   |                 | 4.11.1.5 Analysis                                          |  |  |

|   | 4.12            | Conclusion                                                 |  |  |

| _ |                 |                                                            |  |  |

| 5 |                 | I Preemption Performance Study 81                          |  |  |

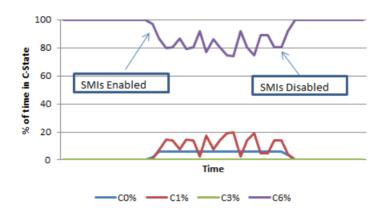

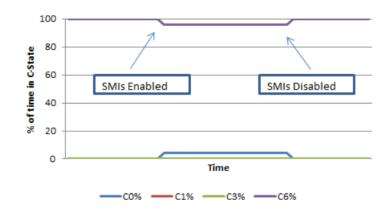

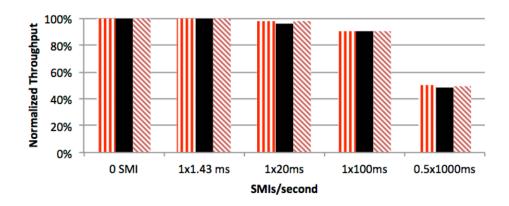

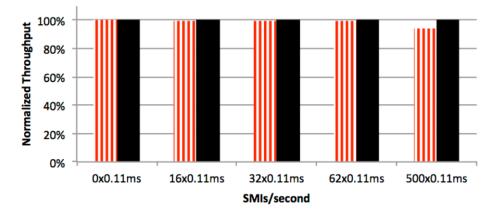

|   | 5.1             | System-level Effects                                       |  |  |

|   |                 | 5.1.1 Timing Expectations in Code                          |  |  |

|   |                 | 5.1.2 Symptoms of Excessive Time Spent in SMM 82           |  |  |

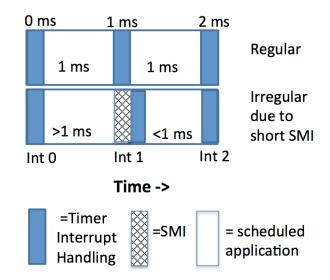

|   |                 | 5.1.3 Timer Interrupt Effects                              |  |  |

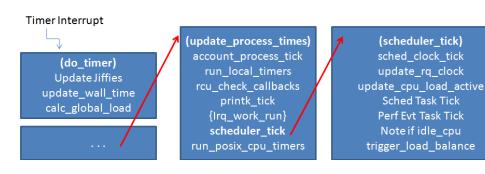

|   |                 | 5.1.3.1 Timer Interrupt Background                         |  |  |

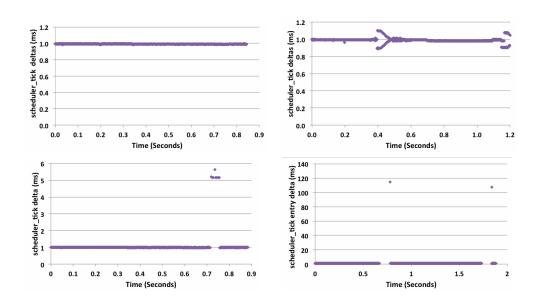

|   |                 | 5.1.3.2 Kernel Instrumentation                             |  |  |

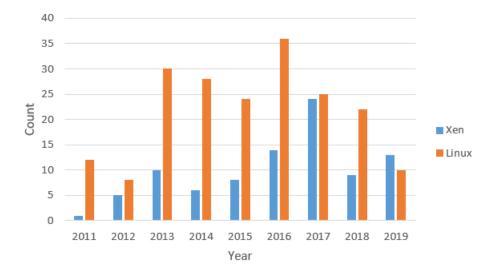

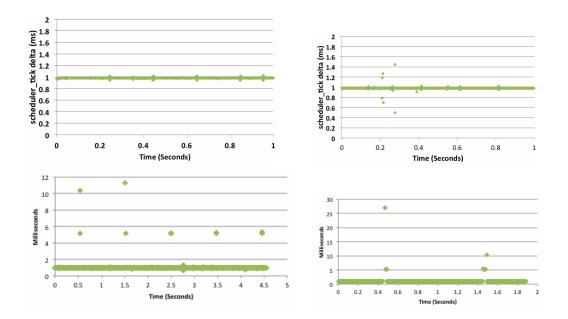

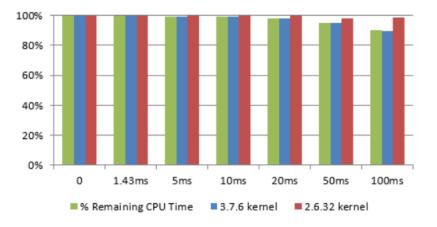

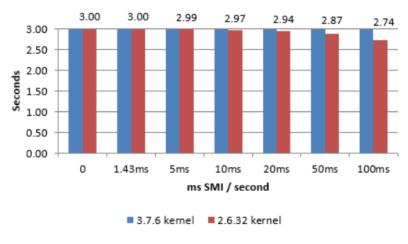

|   |                 | 5.1.3.3 Timer Interrupt Results: Non-virtualized Linux 86  |  |  |

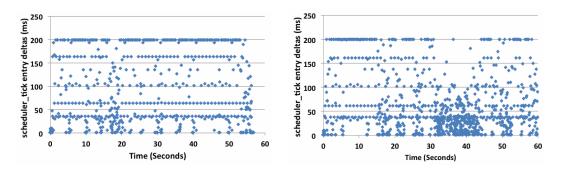

|            |                                                                           | 5.1.3.4<br>5.1.3.5                                                                                                                                                                                                                                                                  | Timer Interrupt Results: Xen Virtualization .<br>Timer Interrupt and Turbostat Results: Tick-                                                                                                                                                                                                                                                                                                                                                                                                                            | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                                           |                                                                                                                                                                                                                                                                                     | less Linux Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            |                                                                           | 5.1.3.6                                                                                                                                                                                                                                                                             | Timer Tick Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | 5.1.4                                                                     | Process                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | 5.1.5                                                                     |                                                                                                                                                                                                                                                                                     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

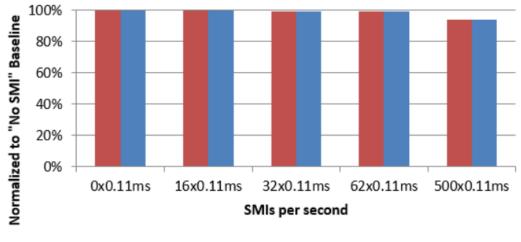

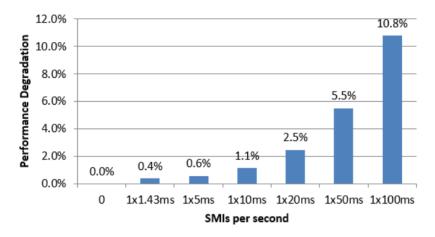

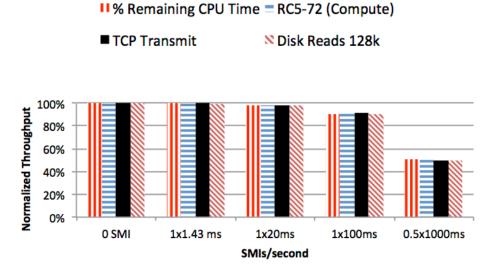

| 5.2        | Appli                                                                     |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | 5.2.1                                                                     |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | 5.2.2                                                                     |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | 5.2.3                                                                     |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.3        |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | -                                                                         |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           | -                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.9        | Concl                                                                     | usions .                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Arc        | hitectu                                                                   | re                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

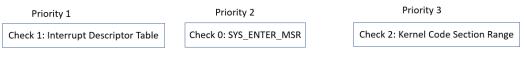

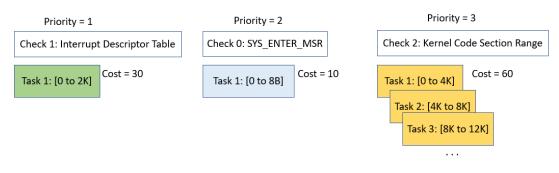

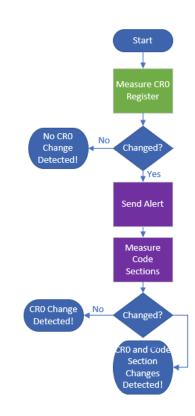

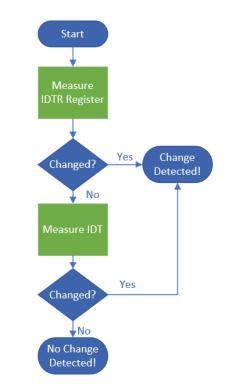

| 7.1        | EPA-F                                                                     | RIMM Ch                                                                                                                                                                                                                                                                             | ecks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 7.1.1                                                                     | Check I                                                                                                                                                                                                                                                                             | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 7.1.2                                                                     | Measure                                                                                                                                                                                                                                                                             | ement Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           | 7.1.2.1                                                                                                                                                                                                                                                                             | Command: Measure Memory Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                                                                           |                                                                                                                                                                                                                                                                                     | Command. Measure Memory Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                           | 7.1.2.2                                                                                                                                                                                                                                                                             | , 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                                                                           | 7.1.2.2<br>7.1.2.3                                                                                                                                                                                                                                                                  | Command: Sample Memory Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 116<br>116<br>117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

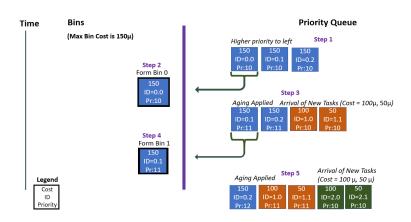

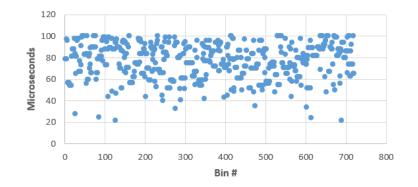

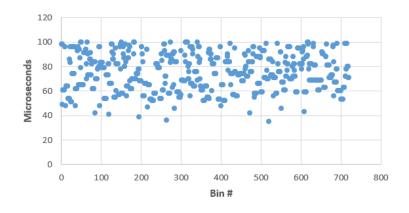

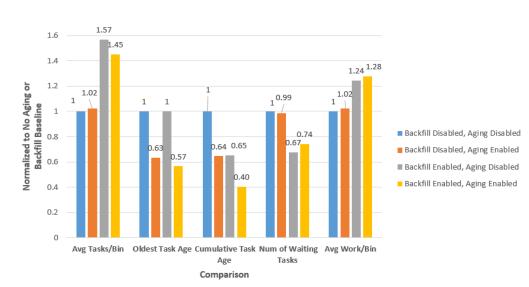

|            |                                                                           |                                                                                                                                                                                                                                                                                     | , 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |