Portland State University PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

3-5-2021

# Memristor Crossbar Array Testing Using Sneak Paths

Rasika Dhananjay Joshi Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Electrical and Computer Engineering Commons Let us know how access to this document benefits you.

#### **Recommended Citation**

Joshi, Rasika Dhananjay, "Memristor Crossbar Array Testing Using Sneak Paths" (2021). *Dissertations and Theses*. Paper 5647. https://doi.org/10.15760/etd.7519

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

Memristor Crossbar Array Testing Using Sneak Paths

by

Rasika Dhananjay Joshi

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

> Dissertation Committee: John M Acken, Chair Marek Perkowski Dan Hammerstrom Steven Bleiler

Portland State University 2021

© 2021 Rasika Dhananjay Joshi

#### Abstract

Moore's law decline has paved the way to shift to new technologies at architectural and device levels. CMOS based technologies are facing many challenges with the growing demand for miniaturization. The growing heat dissipation is the major limitation for performance, energy efficiency and reliability with the increasing transistor count in integrated circuits. Manufacturing costs and process/memory performance gap have also grown steadily over the last several decades with the scaling down of the CMOS feature size. Memristor, a nanoscale device, has the potential to address the CMOS limitations because of its non-volatility, high density, low power operation, low cost per bit and CMOS compatibility.

The high density memristor crossbar structures are widely considered for performing memory operations, logic, stochastic and neuromorphic computations. However, these memristor based devices are prone to defects because of the non-deterministic nature of nano-scale fabrication. The motivation of my research is to develop an application independent methodology for testing memristor circuits for fault detection and fault diagnosis using a unique property of memristor crossbar circuits – sneak paths. Sneak paths are paths for current parallel to the intended path occurring in memristor crossbar architectures. This research characterizes sneak paths and sneak path currents as a function of size of the array, resistance values, input voltage and I/O switch vector. The equations I derived enable us to predict the sneak paths and sneak path currents for various array sizes to determine the constraints to resistive memristor circuits. The sneak path characterization work provides boundary conditions for applications that use memristor

crossbar arrays and provides insights into memristor crossbar testing. Using this characterization, a fault detection method is presented in the dissertation for fault detection of stuck-at low resistance and stuck-at high resistance faults using long sneak paths to result in shorter test vector sets. Long length sneak paths that enable fault detection with shorter test vector sets leads to improved test time. As the crossbar array size increases, the length of the longest possible sneak paths would also increase leading to improved test time compared to March testing. My fault diagnosis method using fault dictionary approach with improved test time is another highlight of this research. The results were demonstrated using LTspice simulations on resistive memristor crossbar circuits by varying resistance programming, IO switch-vectors, input voltage and size of the array.

The fault detection approach used for stuck-at LRS and stuck-at HRS fault detection is extended to test intermediate faults in memristor crossbar circuits. The method of selecting the detection limit for testing intermediate faults in crossbar circuits is presented in the dissertation using crossbar array simulations.

## Dedication

To Aai, Baba, Shubhu, for their unconditional love and guidance throughout To Sarvesh, for his constant support and encouragement To the Almighty Lord Ganesh and Swami Samartha for giving me this opportunity

#### Acknowledgements

First and foremost, I would like to thank my advisor Dr. John M Acken for teaching me to be a researcher. His constant support and guidance throughout the study made it possible for me to reach this step in my academic career. His immense knowledge and patience have always inspired me and brought out the best in me. His continuous motivation and enthusiasm made this experience enjoyable and memorable for me. Thank you, Dr. Acken, for always believing in me.

I would like to thank my other committee members Dr. Perkowski, Dr. Hammerstrom and Dr. Bleiler for their valuable guidance and encouragement.

I would like to thank my husband Sarvesh without whom I would not have reached this step. His continuous support, encouragement and insightful discussions throughout the study were priceless. Thank you Sarvesh for being there for me always.

I would like to thank my parents for providing me all the educational opportunities, for always motivating me and for supporting me whenever I needed it. Thank you Aai, Baba and my brother Shubhu for your endless sacrifices and unconditional love for me. I would like to specially thank my mother for motivating me to pursue a Doctorate and without her I would not have reached this step. I would like to thank my in-laws as well for their continuous support and encouragement.

Last but not the least, I would like to thank Intel Corporation for supporting my study and for providing me with the opportunity to gain deeper understanding in my field of research. I am thankful to my managers and colleagues for their support and enthusiasm for my study.

# Table of Contents

| Abstract                                                                       | i    |

|--------------------------------------------------------------------------------|------|

| Dedication                                                                     | iii  |

| Acknowledgements                                                               | iv   |

| List of Tables                                                                 | viii |

| List of Figures                                                                | ix   |

| Chapter 1 Background and Motivation                                            | 1    |

| 1.1 Introduction                                                               | 1    |

| 1.2 Motivation for research                                                    | 2    |

| 1.3 Research Goals                                                             | 2    |

| 1.4 Dissertation Structure                                                     | 3    |

| Chapter 2 Introduction to Memristors and Memristor Crossbar Arrays             | 5    |

| 2.1 Memristor Introduction                                                     | 5    |

| 2.2 Memristor Write and Read Operations                                        | 8    |

| 2.3 Crossbar Arrays                                                            | 10   |

| 2.3.1 Types of Memristor Crossbars                                             | 11   |

| 2.3.2 Crossbar Applications                                                    | 12   |

| 2.4 Memristor Models                                                           | 19   |

| 2.5 Summary of Chapter 2                                                       | 22   |

| Chapter 3 Sneak Path Characterization in Memristors                            | 24   |

| 3.1 Introduction to Sneak Paths                                                | 24   |

| 3.2 Definition of IO switch-vector                                             | 25   |

| 3.3 Sneak Path Formula for number of sneak paths in crossbar arrays            | 26   |

| 3.4 Analysis on Length of Sneak paths in crossbar arrays                       | 27   |

| 3.5 Analysis of Sneak Path Currents in Crossbar Arrays                         | 34   |

| 3.6 Sneak Path Current Analysis w.r.t size of array and resistance programming | 37   |

| 3.6.1 Resistance Programming                                                          | 37 |

|---------------------------------------------------------------------------------------|----|

| 3.6.2 Sneak Path Current for IO switch-vector $m_{closed} = n_{closed} = 1$           | 39 |

| 3.6.3 Sneak Path Current for IO switch-vector $m_{closed} = m-1$ , $n_{closed} = n-1$ | 41 |

| 3.6.4 Sneak Path Current for IO switch-vector $m_{closed} = 1$ , $n_{closed} = n-1$   | 43 |

| 3.6.5 Sneak Path current ranges                                                       | 45 |

| 3.6.6 Sneak Path current analysis as a function of Resistance                         | 46 |

| 3.6.7 Sneak path current analysis in comparison with the Primary current path .       | 48 |

| 3.6.8 Line Resistance impact on sneak path current                                    | 50 |

| 3.7 Summary of Chapter 3                                                              | 50 |

| Chapter 4 Review of Testing Resistive Memristor Crossbar Arrays                       | 52 |

| 4.1 Faults in memristor circuits                                                      | 52 |

| 4.2 Currently Published testing methodologies for Fault Detection                     | 55 |

| 4.3 Fault Diagnosis                                                                   | 67 |

| 4.3.1 Fault Diagnosis methodologies                                                   | 68 |

| 4.4 Drawbacks of existing testing methodologies                                       | 73 |

| 4.5 Research Goals for testing memristor circuits                                     | 74 |

| 4.5.1 Research Goal 1: Fault Coverage                                                 | 74 |

| 4.5.2 Research Goal 2: Fault Detection                                                | 77 |

| 4.5.3 Fault Detection Using Sneak Paths                                               | 78 |

| 4.5.4 Research Goal 3: Fault Diagnosis using Sneak Paths                              | 79 |

| 4.5.5 Research Goal 4: Test Pattern Generation                                        | 79 |

| 4.6 Summary of Chapter 4                                                              | 79 |

| Chapter 5 Sneak Path based testing in Memristor circuits                              | 80 |

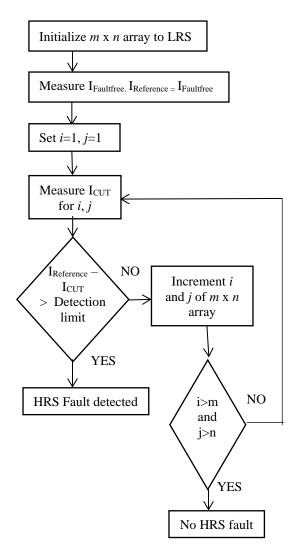

| 5.1 Stuck-at LRS and Stuck-at HRS faults                                              | 80 |

| 5.2 Fault Detection Approach                                                          | 81 |

| 5.2.1 Fault Detection Example Using Sneak Paths                                       | 82 |

| 5.3 Fault Diagnosis Methodology Using Sneak Paths                                     | 84 |

| 5.4 Fault Coverage using sneak path testing                                           | 90 |

| 5.5 Summary of Chapter 5                                                              | 94 |

| Chapter 6 Detection Limit for Intermediate Faults            |     |

|--------------------------------------------------------------|-----|

| 6.1 Intermediate faults                                      |     |

| 6.2 Fault Detection Method for Intermediate Faults           |     |

| 6.2.1 Fault detection example for Intermediate faults        |     |

| 6.2.2 Current resolution for Fault detection measurement     | 103 |

| 6.3 Summary of Chapter 6                                     | 105 |

| Chapter 7 Summary, Conclusions, Achievements and Future Work | 106 |

| 7.1 Summary and Conclusion                                   | 106 |

| 7.2 Achievements and Publications                            | 108 |

| 7.3 Future Work                                              | 109 |

| References                                                   | 110 |

| Appendix: Source code Listing                                |     |

### List of Tables

| Table 1 Count of Possible Different Length Sneak Paths in Crossbar Circuits            | 32 |

|----------------------------------------------------------------------------------------|----|

| Table 2 Low and High Resistance Values for Memristors                                  | 38 |

| Table 3 Primary Current and Sneak Path Current Comparison                              | 49 |

| Table 4 Memristor Faults                                                               | 53 |

| Table 5 Defect Classification in Hybrid memory [55]                                    | 65 |

| Table 6 Test sequence and faults detected by each sequence for fault diagnosis [57]    | 70 |

| Table 7 Fault dictionary of March-MD [53]                                              | 73 |

| Table 8 Diagnosis example when first test vector fails for 3x3 memristor array         | 88 |

| Table 9 Diagnosis example when first vector passes for 3x3 memristor array             | 90 |

| Table 10 Five memristor long sneak paths in 3x3 memristor array                        | 93 |

| Table 11 Memristor Faults                                                              | 97 |

| Table 12 Sneak Path current analysis for Intermediate faults in a 3x3 crossbar array 1 | 00 |

# List of Figures

| Fig. 1 Fourth missing element [2]                                                          |

|--------------------------------------------------------------------------------------------|

| Fig. 2 a) TiO <sub>2</sub> thin film memristor structure b) equivalent circuit [4] 6       |

| Fig. 3 Hysteresis Loop [5]                                                                 |

| Fig. 4 (a) Memristor output levels, and (b) memristor 3D nano-structure [6]9               |

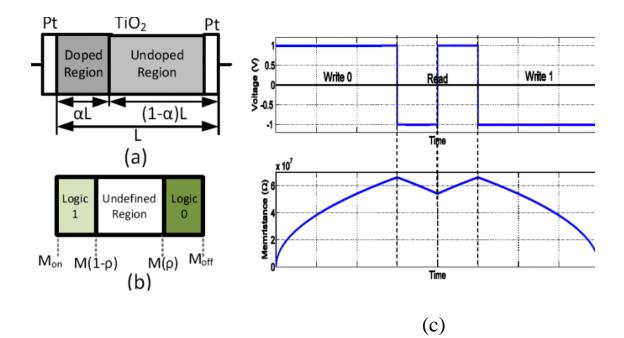

| Fig. 5 a) Memristor model, (b) Memristance range for different logic levels, and (c)       |

| Variation of memristance due to voltage over time [7] 10                                   |

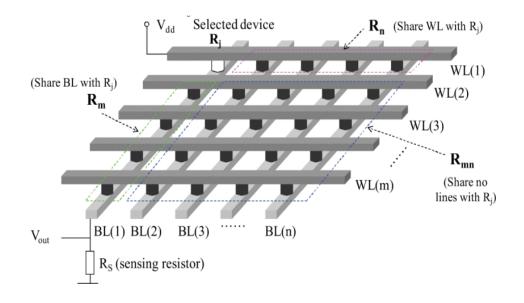

| Fig. 6 Crossbar array with $m$ WLs (horizontal line) and $n$ BLs (vertical lines). $Rj$ is |

| selected cell. Rn, Rm are half-selected devices and Rmn is unselected device sharing no    |

| line with <i>Rj</i> [8]                                                                    |

| Fig. 7 Proposed 2M1M crossbar memory architecture [10]14                                   |

| Fig. 8 Application of memristor crossbars for vector-matrix multiplication [14] 15         |

| Fig. 9 Schematic of write-time memristive PUF circuit [25] 17                              |

| Fig. 10 ReVAMP Architecture [26]                                                           |

| Fig. 11 Physical memristor structure based on the Simmon tunnel barrier model. W and       |

| $R_s$ represent the tunneling barrier width and electroformed channel resistance           |

| respectively. S, A, and V represents the voltage source, ammeter, and voltmeter            |

| respectively [31]                                                                          |

| Fig. 12 Ideal case of current flow through a memristor cell and sneak path flow of         |

| current in a crossbar array                                                                |

| Fig. 13 3x3 Crossbar array with I/O switch-vector = 100100                                 |

| Fig. 14 Circuit diagram for 3x3 memristor array with I/O switch-vector = 100100 29         |

| Fig. 15 Sneak paths of length 3 in a $3x3$ crossbar array with I/O switch vector = 100100                     |

|---------------------------------------------------------------------------------------------------------------|

|                                                                                                               |

| M1c=M2b=M3a=HRS and remaining memristors in LRS for I/O switch vector =100100.                                |

|                                                                                                               |

| Fig. 17 Sneak Path current analysis for one input ON and one output ON $[m_{closed} = n_{closed}]$            |

| =1] for LRS programming of $10K\Omega$ where m=n                                                              |

| Fig. 18 Sneak Path current analysis for one input ON and one output ON for $[m_{closed} =$                    |

| $n_{closed} = 1$ ] HRS programming of 500K $\Omega$ where m=n                                                 |

| Fig. 19 Sneak Path current analysis for m $-1$ inputs ON and n $-1$ outputs ON [m <sub>closed</sub> = m-      |

| 1] for LRS programming of $10K\Omega$ where m=n                                                               |

| Fig. 20 Sneak Path current analysis for m–1 inputs ON and n–1 outputs ON $[m_{closed} = m - 1]$               |

| 1] for HRS programming of $500 \text{K}\Omega$ where m=n                                                      |

| Fig. 21 Sneak Path current analysis for single input ON and all outputs ON except one                         |

| $[m_{closed} = 1 \text{ and } n_{closed} = n-1]$ for HRS and LRS programming of 50K $\Omega$ and 10K $\Omega$ |

| respectively                                                                                                  |

| Fig. 22 Sneak Path current analysis with variation in I/O switch-vector ( $m_{closed} = 1$ and                |

| n <sub>closed</sub> =1,2,3,4,5) for 6x6 crossbar array for 10K resistance programming                         |

| Fig. 23 Sneak Path current analysis for one input ON and one output ON $[n_{closed} = m_{closed}]$            |

| =1] for LRS and HRS programming of resistances in Table 2 where n=m                                           |

| Fig. 24 RoD current variation for stuck-at Fault detection [5] Redrawn                                        |

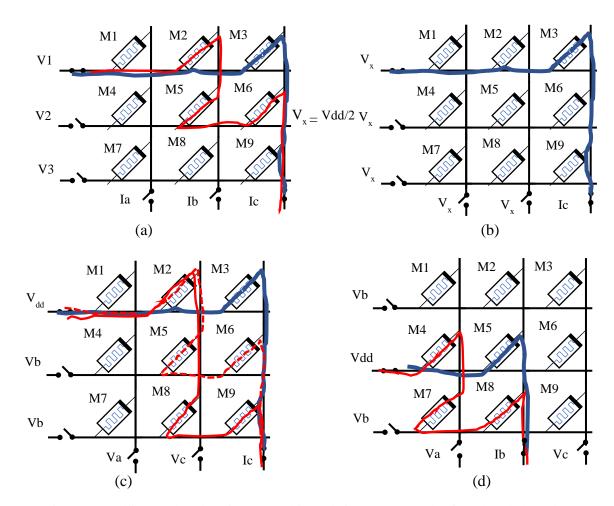

| Fig. 25 Controlling sneak paths using voltage bias technique: (a) Example of sneak path                       |

| through M2, M5 and M6 highlighted in red (b) sneak-path elimination with an uniform                           |

| level of voltage bias $V_x$ applied to wordline/bitlines; (c)Two sneak paths in red with    |

|---------------------------------------------------------------------------------------------|

| intended memristor as M3 (d) Sneak path highlighted in red with intended memristor          |

| changed to M5 [9]. [Redrawn]59                                                              |

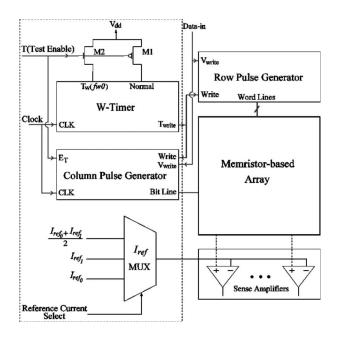

| Fig. 26 Programmable DFT scheme [52]61                                                      |

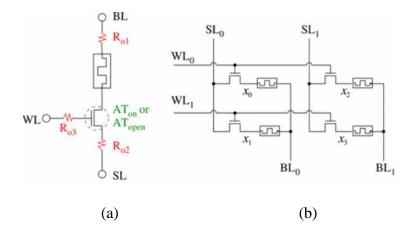

| Fig. 27 (a) Possible open, transistor stuck-on, transistor stuck-open defects in a 1T1R     |

| cell. (b) A 2×2 1T1R cell array [50]                                                        |

| Fig. 28 Electrical equivalent circuit [55] 64                                               |

| Fig. 29 Divide and Conquer approach [56]67                                                  |

| Fig. 30 Diagnosis process: (a) Example current in the RoD; (b) Diagnosis process for        |

| single fault in RoD [9]68                                                                   |

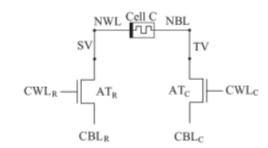

| Fig. 31 Rnv8T SRAM cell structure [53]72                                                    |

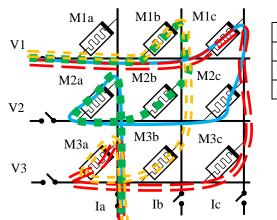

| Fig. 32 Sneak paths of length 5 in a $3x3$ crossbar array with M1c=M2b=M3a = HRS and        |

| all of the rest of the memristors in LRS and for IO switch-vector = 10010075                |

| Fig. 33 Sneak paths of length 5 in a $3x3$ crossbar array with M1c=M2b=M3a = HRS and        |

| all of the rest of the memristors in the LRS and for I/O switch-vector = 100100             |

| Fig. 34 Stuck-at LRS fault example for single step of march testing in a 3X3 crossbar       |

| array77                                                                                     |

| Fig. 35 Fault Detection Using Sneak Paths in a 3x3 crossbar array                           |

| Fig. 36 Fault Detection for HRS Fault                                                       |

| Fig. 37 Fault detection for LRS fault                                                       |

| Fig. 38 Sneak paths of length 3 in a $3x3$ crossbar array with I/O switch vector = $100100$ |

|                                                                                             |

| Fig. 39 Fault Diagnosis Methodology for LRS/HRS faults                                      |

| Fig. 40 Sneak path M1b-M3b-M3c-M2c-M2a of length five in a 3x3 crossbar array with        |

|-------------------------------------------------------------------------------------------|

| M1c=M2b=M3a=HRS and remaining memristors in LRS for I/O switch vector =100100.            |

|                                                                                           |

| Fig. 41 Sneak path M1c-M2c-M2b-M3b-M3a of length five in a 3x3 crossbar array with        |

| M1b=M2a=M3c=HRS and remaining memristors in LRS for I/O switch vector =100100.            |

|                                                                                           |

| Fig. 42 Sneak Path current for fault free and intermediate faults in a 3x3 crossbar array |

|                                                                                           |

| Fig. 43 Three memristor long sneak paths in 3x3 crossbar array with IO switch vector      |

| =100100 with all memristors in HRS                                                        |

#### Chapter 1

#### **Background and Motivation**

#### 1.1 Introduction

CMOS technology is fast approaching its fundamental limitations with the growing demand for miniaturization. Excessive heat dissipation and increasing fabrication cost are primary concerns as the transistor density on the chip increases. The memory wall problem where the memory latency and bandwidth become insufficient for instruction and data transfers to the processor is also more prominent with the ever-increasing amount of data computations using conventional microelectronics technology. Conventional memory technologies such as Flash, DRAM, and SRAM are not able to keep up with the demand for scaling and low power. Memristor, an emerging nanoscale device, has the potential to address these issues in the near future.

In 1971, Leon Chua predicted the existence of a fourth fundamental element (the other three electrical elements are resistor, capacitor, and inductor) known as the memristor (short for memory resistor) [1]. Although he showed that such an element has interesting and useful circuit properties, no one presented a physical model or example of the memristor until 2008. R.S. William's team in Hewlett Packard Labs [2-3] then came up with a simple analytical example of memristance in thin film nanoscale devices. Memristors are one of the promising alternatives for next-generation memory technology due to their non-volatility, high density, low power operation, low cost per bit and CMOS compatibility. Memristor technology has become an attractive option for use in memory architectures, in-memory computing, logic, and neuromorphic applications. Memristor

devices find a broad range of applications in both analog and digital domains. Several research efforts have focused on expanding the memristor technology in the areas of design, test, memories, and memristor architectures for various applications. Crossbar structures are used for many of these applications for performing logic, memory, security, and stochastic computations.

#### 1.2 Motivation for research

Nanoscale memristor devices are prone to defects due to the non-deterministic nature of nanoscale fabrication. It is necessary to test memristor devices for detecting memristor faults and to diagnose the location of such faults. Providing high quality and efficient test solutions is of great importance to enable the commercialization of memristor devices. The motivation behind my research is to generate a good quality testing methodology for memristor crossbar arrays that is application-independent. For example, the methodology will work for testing RRAM applications, for logic computations, neuromorphic applications and for user authentication systems etc.

#### 1.3 Research Goals

My research focuses on analyzing the unique properties of memristor crossbar arrays specifically, sneak paths and sneak path currents for testing memristor circuits. Sneak paths are defined as current paths parallel to the target memristor path. My research work characterizes sneak path length and sneak path current as a function of the size of the array, memristor resistance values, input voltage and IO switch-vector. The sneak path characterization work provides boundary conditions for applications that use memristor crossbar arrays and provides insights into memristor crossbar testing. A testing technique for memristor fault detection and fault diagnosis using sneak paths is proposed using the sneak path characterization work. The advantage of using a sneak path testing scheme is that multiple memristors can be tested at the same time by exploiting sneak path currents in crossbar arrays. Sneak path testing helps to reduce test time compared to the conventional March memory tests that target only one memristor device at a time, which consumes a lot of test time. My proposed testing technique addresses single stuck-at low resistance faults, single stuck-at high resistance faults and intermediate faults in memristor circuits. A new fault terminology, "intermediate faults" has been introduced that covers memristor resistances falling between low resistance and high resistance limits. The contributed test methodology aims to improve test time by proposing shorter tests by optimizing the set of IO test vectors and memristor resistance programming for a given size of the array. My research contribution includes the analysis of setting the right detection limit for detecting intermediate faults along with stuck-at low resistance and stuck-at high resistance faults.

#### 1.4 Dissertation Structure

The dissertation is organized as follows. This chapter describes the introduction to memristor technology, the motivation behind the research and the research goals. Chapter 2 reviews memristor theory, crossbar arrays and their applications and memristor models. Chapter 3 describes sneak paths and sneak path currents in memristor circuits. This chapter also discusses my published sneak path characterization work in memristor crossbar circuits. Chapter 4 reviews test methodologies referenced in literature for testing

memristor circuits. The conclusions from these reviewed test methodologies are presented and my research objectives are discussed. Chapter 5 presents my published work for testing memristor faults in crossbar circuits using sneak paths for stuck-at low resistance and stuck-at high resistance faults. Chapter 6 extends the fault detection methodology used for stuck-at LRS and stuck-at HRS faults for testing intermediate faults in memristor circuits. It discusses my published work for analysis of setting the detection limit for intermediate fault detection in memristor crossbar circuits. Chapter 7 summarizes the contributions and conclusions of the dissertation. In addition, publications and future work are also discussed in this chapter.

#### Chapter 2

#### Introduction to Memristors and Memristor Crossbar Arrays

#### 2.1 Memristor Introduction

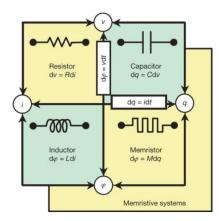

The existence of the memristor was first theorized by Leon Chua in 1971 [1]. It was called the fourth missing element among the other three fundamental elements, namely resistor, capacitor, and inductor. These three two-terminal circuit elements already have established relationships between pairs of the four fundamental circuit variables, namely the current *i*, voltage *v* and charge *q*, and the flux-linkage  $\varphi$ . Chua noted that the number of equations connected to these pairs of circuit variables are six. Two of these relationships are defined by dq = i and  $d\varphi = v$ . Three other relationships are defined by namely, resistor (the relationship between *v* and *i*), the inductor (the relationship between  $\varphi$  and *i*), and the capacitor (the relationship between *q* and *v*). Chua invented the missing relationship between flux and charge as  $d\varphi=Mdq$  where M is the memristance of the device as shown in Fig.1.

Fig. 1 Fourth missing element [2]

A memristor is a two-terminal passive resistive device whose resistances vary based on the history of voltages applied to it. In simple words, if a positive voltage is applied to the undoped end of this two-terminal passive device, the resistance decreases and if a negative voltage is applied, the resistance increases. The memristance (M, measured in Ohms) of the device is determined by the voltage V applied between the terminals as a function of time. The M of the device is expressed as shown in (1).

$$M = v(t)/I(t) \tag{1}$$

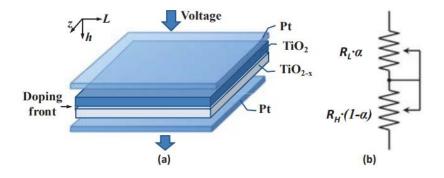

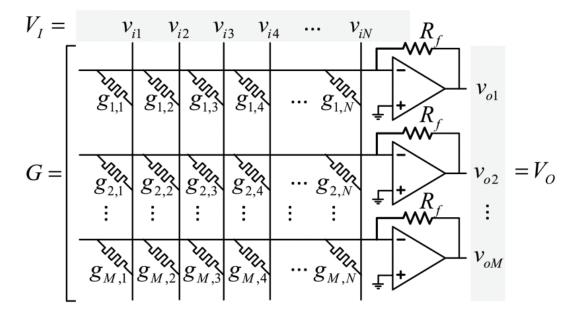

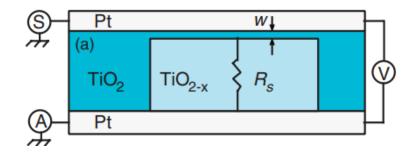

HP labs [2] developed memristors which consisted of 50-nm wide Titanium Oxide (TiO<sub>2</sub>) thin film sandwiched between two platinum wires as seen in Fig. 2. This film consisted of two zones: First, un-doped low conductivity zone with an exact 2:1 ratio of oxygen to titanium. Second, doped high conductivity zone with oxygen deficient  $TiO_{2-x}$ . The memristor is modeled as two variable resistors connected in series. An internal state variable of the memristor denoted by " $\alpha$ " is equivalent to the ratio of the length of the doped region to the total width of the thin film.

Fig. 2 a) TiO<sub>2</sub> thin film memristor structure b) equivalent circuit [4]

Applying a positive voltage (v(t) > 0) at the undoped end of the memristor lowers the resistance of the memristor due to the drifting operation of the oxygen vacancies into the un-doped region. Similarly, applying a negative voltage (v(t) < 0) increases the overall resistance of the memristor since now the oxygen vacancies drift in the opposite direction. Low resistance state (LRS)  $R_{on}$  occurs when  $\alpha=0$  and high resistance state (HRS)  $R_{off}$  when  $\alpha=1$ . Thus, the total memristance M of the memristor is expressed in (2)

$$M(\alpha) = \alpha R_{on} + (1 - \alpha) R_{off}$$

<sup>(2)</sup>

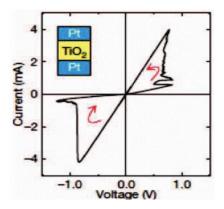

The different memristance values exhibited by the memristor are used to represent different logic values. The memristor shows a non-linear behavior between the input voltage V and output current I. The hysteresis loop is shown in Fig. 3. The loops show the switching behavior of the device: it begins with a high resistance, and as the voltage increases, the current slowly increases. As charge flows through the device, the resistance drops, and the current increases more rapidly with increasing voltage until the maximum is reached. The result is an on-switching loop. When the voltage turns negative, the resistance of the device increases, resulting in an off-switching loop. Thus, the application of a positive bias voltage to the device leads to the switching of the resistance states from the High to the Low state, this switching is labeled as SET. A RESET switching corresponds to the exchange from the LRS to HRS state.

Fig. 3 Hysteresis Loop [5]

#### 2.2 Memristor Write and Read Operations

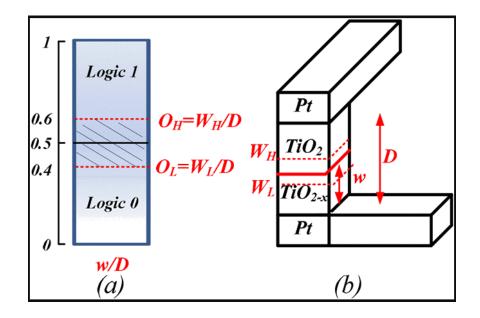

The internal state variable of the memristor denoted by "w(t)/D" is equivalent to the ratio of the length of the doped region "w" to the total length of the TiO<sub>2</sub> film "D". The memristor can be defined at logic 0 when 0 < w(t)/D < 0.5 and logic 1 when 0.5 < w(t)/D < 1.0. The corresponding ideal output low and high levels are w(t)/D=0 and w(t)/D=1, respectively. In reality, to account for possible noise injections, a safety margin is left for each logic output:  $0 \le w/D \le O_L$ , ( $O_L = W_L/D < 0.5$ ) for logic 0, and  $O_H \le w/D \le 1.0$ ( $O_H = W_H/D > 0.5$ ) for logic 1. The region in between  $O_L \le w/D \le O_H$  is an intermediate region that should be avoided for strict logic value read-write data integrity. Fig. 4 shows the situation where  $O_L = 0.4$  and  $O_L = 0.6$ .

Fig. 4 (a) Memristor output levels, and (b) memristor 3D nano-structure [6]

#### 1) Memory write operation:

A positive voltage is applied across the memristor for a fixed duration to write a logic 1. The duration of the pulse should be long enough to decrease the memristance from the logic 0 region to the logic 1 region. Similarly, to write a logic 0, a negative voltage is applied across the device long enough for the memristance to increase from the logic 1 region to the logic 0 region.

#### 2) Memristor Read Operation:

Applying a voltage across the memristor causes the dopants to drift and change its memristance. To ensure that the resistance of the memristor is not changed during the read operation, a two-stage read operation is used [6]: Convert stage and sense amplifier stage. The convert stage is implemented by adding a series resistor to the memristor to convert the memristor state into a voltage signal since the current through the memristor carries the memristor state information. The second stage is to have a read pulse width limit so that the memristance does not move beyond the safety margin. Fig. 5(c) shows the ideal read pattern is a negative pulse followed immediately by a positive pulse with the same magnitude and duration, creating a zero net change in memristance.

Fig. 5 a) Memristor model, (b) Memristance range for different logic levels, and (c) Variation of memristance due to voltage over time [7]

#### 2.3 Crossbar Arrays

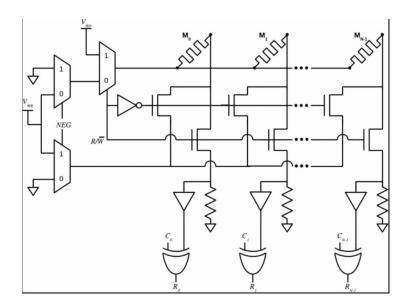

A crossbar array is a typical structure for many memristor implementations including memristor-based memories. Fig. 6 shows the schematic representation of a crossbar array with m wordlines (WLs) and n bitlines (BLs). It employs a memristor device at each intersection of horizontal and vertical metal wires without any selectors. A set of input voltages is applied on the word-lines (WLs) of the array and the output current is measured through each bit-line (BL). The device at the upper left corner (Rj) is the selected cell at

the intersection of the selected wordline and bitline. Unselected devices can be divided into three groups depending on whether they share an access line with Rj. Devices sharing a line with Rj are also called "half-selected" devices. Rn shares WL with Rj and Rm shares a BL with Rj. These are half-selected cells. Rmn shares no line with Rj; hence it is called as the unselected cell.

Fig. 6 Crossbar array with m WLs (horizontal line) and n BLs (vertical lines). Rj is selected cell. Rn, Rm are half-selected devices and Rmn is unselected device sharing no line with Rj [8].

#### 2.3.1 Types of Memristor Crossbars

The generic structure of the memristor crossbar array is a 1M crossbar structure where the memristor devices are located at the intersection of each wordline and bitline of the array. The 1R-RRAM [9] resistive crossbar is an example of this structure that offers very high data density for data storage applications. The other crossbar structure commonly used is the 1T1R where a selector device, for example an access transistor is associated with the

memristive device. 1T1R [7] designs help eliminate sneak paths in the crossbar arrays but do not offer the same density as the 1R structure. Recently, a 2M-1M crossbar architecture has been proposed where each memristor cell has two access memristors and one target memristor [10]. 1D1R [11][12] structure is also used to suppress crosstalk by using external diodes. Rectifying memristors [13] have replaced the 1D1R structure due to its intrinsic diode-like behavior to suppress sneak paths. My research concentrates on resistive single memristive cell crossbar arrays (1M crossbar structure) to take advantage of sneak paths for testing memristor circuits.

#### 2.3.2 Crossbar Applications

Researchers have made numerous efforts and initiatives to propose new crossbar architectures that offer high density, low energy consumption, low sneak path current effect and low wiring to outperform conventional memories. For example, the memristor-based memory cell can be utilized for high density memory and logic applications [10]. Another example is the multi-crossbar memristor architecture as an accelerator for matrix multiplications and handwriting recognition. This architecture achieves high speed and energy savings for 64x64 matrix multiplications [14]. Memristor crossbars have also been applied in user authentication systems [15], Resistive Random-Access Memories [RRAM] arrays [16], parallel computations [17], logic operations [18], neuromorphic systems [19] and Physically Unclonable Functions (PUFs) [20-21]. In summary, crossbar structures are used for many applications including logic, memory, stochastic computation, security PUFs, and neuromorphic applications.

Some of the crossbar array applications are discussed in this section.

#### 1) 2M1M Crossbar Architecture: Memory [10]

This research in [7] presents a 2M1M crossbar architecture capable of memory and logic applications that provides a high area density in comparison with the state-of-the-art memristive memory architectures. It is a pure memristor-based memory cell and does not need CMOS transistors within the crossbar structure as seen from Fig. 7. The main advantages of this type of architecture are as follows:

- The read and write operations are done by the same memristor circuits without the need for additional circuitry within the memory fabric. Thus, the number of required elements is significantly reduced, simplifying the crossbar structure.

- The reading method does not need isolated access to the memristor node which reduces circuit wiring and leads to a very simple structure with less complexity.

- The proposed structure provides an effective gating mechanism by which memory elements can be partially isolated from the access line during the reading cycle, which considerably reduces the sneak path currents compared to its memory peers.

- The proposed memory structure provides acceptable speed and energy consumption in comparison with state of the art. Also, it has a higher density and less alternate current path effect comparing with its peer.

Fig. 7 Proposed 2M1M crossbar memory architecture [10]

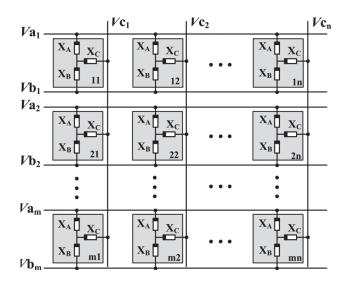

#### 2) Code Acceleration Using Memristor-Based Approximate Matrix Multiplier [14]

In this paper, the research focuses on building a memristor-based approximate accelerator to be used with general-purpose X86 processors for different applications such as matrix multiplication and handwriting recognition. Fig. 8 gives an overview of the memristor crossbar application for vector-matrix multiplication.  $V_1$  is the input vector voltage to the columns of the crossbar, G is the matrix,  $V_0$  is the output voltage sensed by the transimpedance amplifier with feedback resistor  $R_f$ . The high-level architecture of the proposed accelerator consists of multiple processing units that be used for performing independent computations through the extended instruction set architecture (ISA). These processing units consist of a memristor based crossbar, input-output buffers, and a logic circuit. To set up the accelerator, the program must initialize a processing unit which includes determining the size of the crossbar, configuring memristors' conductance, and determining the type of input numbers. The accelerator is compatible with signed complex number computations and with floating-point arithmetic. To validate the accelerator, it is first utilized to multiply different matrices that vary in size and distribution. It is then used as an accelerator for accelerating the tiny-dnn, an open-source C++ implementation of deep learning neural networks. It provides more than  $100 \times$  speedup and energy saving for  $64 \times$ 64 matrix multiplications.

Fig. 8 Application of memristor crossbars for vector-matrix multiplication [14]

# 3) Automated synthesis of compact crossbars for sneak-path based in-memory computing [22]

The rise of data-intensive computational loads has exposed the processor-memory bottleneck in Von Neumann architectures. It has reinforced the need for in-memory computing using devices such as memristors. Boolean formula computing using sneak-paths in nanoscale memristor crossbars [23][24] suffers from the requirement to arrange memristors in dense nanoscale crossbars for ease of fabrication and the inability to produce compact crossbars for simple Boolean operations. The paper [22] is trying to answer two open questions using sneak paths in memristor crossbars for performing logical

computations: 1) The size estimation of the memristor crossbar that can compute a given Boolean formula using sneak paths 2) Synthesize compact crossbars for computing large Boolean formula using sneak paths. The authors demonstrate that the number of rows and columns required to calculate a Boolean formula is at most linear in the size of the Reduced Ordered Binary Decision Diagram (ROBDD) representing the Boolean function. The authors are the first to suggest the use of ROBDD for synthesizing compact memristor crossbars. They design sneak-path based memristor crossbars for circuits as large as 128bit adders. For their experiments, they relied on HSPICE simulations.

#### 4) Performance analysis of a memristive crossbar PUF design [25]

Physical unclonable functions (PUF) provide a unique hardware identifier where the intrinsic properties of the device are used to create a signature for security concerns including integrated circuit (IC) piracy, counterfeiting and secret key storage. A memristor crossbar based PUF circuit is described in this paper that utilizes variations in the write-time of the memristors as the primary entropy source. The main motivation to use memristor instead of CMOS for PUF designs is a lesser physical area and power dissipation. The proposed XBARPUF crossbar design schematic is shown in Fig. 9.

Fig. 9 Schematic of write-time memristive PUF circuit [25]

The amount of time taken for the memristor to SET during the write operation is the entropy source of the memristive PUF. The PUF circuit relies on the relative write-times of pairs of memristive circuits to generate the response. The write operation is governed by the challenge such that only one memristor in the pair is written at a time. This results in several unique combinations of altered memristors to select from while generating the signature. The sneak path currents in the crossbar design are also used for the response bit analysis. Results demonstrate strong statistical performance in terms of entropy, uniqueness, and uniformity [25].

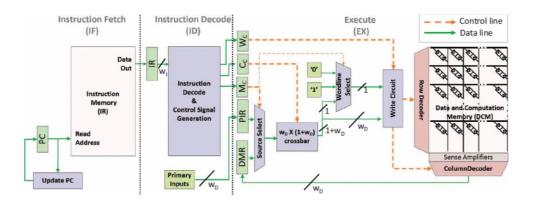

#### 5) *ReVAMP: ReRAM based VLIW architecture for in-memory computing* [26]

A general purpose computing platform has been proposed in this paper [26] that is based on Resistive RAM (ReRAM) crossbar array. This architecture supports VLIW (Very Long Instruction word) instructions to exploit parallelism in the memory array operations. The ReRAM crossbar memory consists of 1S1R ReRAM devices arranged in a crossbar array fashion. Fig 10 shows the ReVAMP (<u>ReRAM</u> based <u>VLIW</u> architecture for in-<u>M</u>emory computing). It has two crossbar memories which are the instruction memory (IM) and Data storage and Computation Memory (DCM). It has a three-stage pipeline with instruction fetch (IF), instruction decode (ID) and execute (EX) stages. The instruction is fetched from the IM in the IF stage at the address held by the program counter. It is then loaded into the instruction register (IR) before the PC is updated. In the ID stage, the instruction is read to provide the inputs to the crossbar interconnect and write circuit.

Fig. 10 ReVAMP Architecture [26]

The DMR (Data Memory Register) stores the data from the DCM. The primary input register (PIR) acts as a primary input data buffer. The crossbar interconnect consists of a set of multiplexers to select the number of wordline and bitline inputs as per the stored control signals. The write circuits in Fig.10 read the output of the crossbar-interconnect to determine the inputs to be applied to the row and column decoder of the DCM. The performance of the architecture is demonstrated in terms of delay, number of words and word utilization on the benchmark set.

#### 2.4 Memristor Models

Several mathematical models of the memristors have been proposed to describe the behavior of memristors. This section will provide a brief description of different memristor models such as the linear ion drift model, the nonlinear ion drift model, and the ThrEshold Adaptive Memristor (TEAM) model.

#### 1) Linear Ion Drift Model

The linear dopant drift model is widely utilized for memristor circuits and it provides a simple and useful approximation for memristor behavior [2]. Considering the TiO<sub>2</sub> memristor device as an example, the physical width D contains two regions, as shown in Fig 1(a). One of these regions has highly doped titanium dioxide with oxygen vacancies (TiO<sub>2-x</sub>) and the other has undoped titanium dioxide (TiO<sub>2</sub>). The device is modeled as two resistors connected in series and the region with the dopants has a higher conductance than the oxide region. The electric field generated through the applied bias is capable of drifting dopants based on the voltage polarity, therefore changing the resistance of the device. Assuming ohmic conductance, linear ion drift in a uniform field and ions having average ion mobility  $\mu_{\nu}$  equations (3) and (4) express the state variable and equivalent resistance

$$\frac{dw}{dt} = \mu_{v} \frac{R_{ON}}{D} i(t) \tag{3}$$

$$\nu(t) = \left(R_{ON} \frac{w(t)}{D} + R_{OFF} \left(1 - \frac{w(t)}{D}\right)\right) \cdot i(t)$$

(4)

where  $R_{ON}$  is the resistance when w(t) = D and  $R_{OFF}$  is the resistance when w(t) = 0. On removing the bias, the dopants retain their place and the resistance of the device is preserved.

#### 2) Non-linear ion drift Model

The behavior of the fabricated memristor device deviates significantly from the linear ion drift model and is very non-linear. Several non-linear ion drift models have been proposed, especially for logic computations [27-28]. Lehtonen [29] proposed a model based on the experimental results described in [30]. Equation (5) describes the relationship between current and voltage for this model.

$$i(t) = w(t)^{n} \beta \sinh(\alpha v(t)) + \chi[\exp(\Upsilon v(t)) - 1]$$

(5)

where  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\chi$  are the experimental fitting parameters and *n* determines the influence of the state variable on the current. This model assumes asymmetric switching behavior and nonlinear dependence on voltage in the state variable differential equation as shown in (6),

$$\frac{dw}{dt} = \alpha \cdot f(w) \cdot v(t)^m \tag{6}$$

where  $\alpha$  and *m* are constants, m is an odd constant and f(w) is a window function. When the device is in ON state, the state variable *w* is close to 1 and  $w = w(t)^n \beta \sinh(\alpha v(t))$ , describing a tunneling phenomenon. When device is in the off-state, the state variable *w* is close to 0 and  $w = [\exp(\Upsilon v(t)) - 1]$ .

#### 3)Simmons tunnel barrier model

In [31], Pickett *at el.* presents a nonlinear memristive model of bipolar switching known as the Simmons tunnel barrier model. The model is derived from the experimental results of a dynamic testing protocol applied to a Pt-TiO<sub>2</sub>-Pt memristor device. In this model, instead of two resistors in series like the HP model, a resistor is in series with the electron tunnel barrier as shown in Fig 11.

Fig. 11 Physical memristor structure based on the Simmon tunnel barrier model. *W* and *R*<sub>s</sub> represent the tunneling barrier width and electroformed channel resistance respectively. *S*, *A*, and *V* represents the voltage source, ammeter, and voltmeter respectively [31].

The model exhibits nonlinear and asymmetric switching behavior due to the exponential dependence of the drift velocity of the ionized dopants on the applied current. In this model, the velocity of the oxygen vacancy drift can be explained by equation (7) for off-switching and (8) for on-switching.

$$\frac{dw}{dt} = f_{off} \sinh\left(\frac{i}{i_{off}}\right) \exp\left[-\exp\left(\frac{w-a_{off}}{w_c} - \frac{|i|}{b}\right) - \frac{w}{w_c}\right]$$

(7)

$$\frac{dw}{dt} = f_{on} \sinh\left(\frac{i}{i_{on}}\right) \exp\left[-exp\left(\frac{w-a_{on}}{w_c} - \frac{|i|}{b}\right) - \frac{w}{w_c}\right]$$

(8)

where  $f_{off}$ ,  $f_{on}$ ,  $i_{off}$ ,  $i_{on}$ ,  $a_{on}$ ,  $a_{off}$ , b and  $w_c$  are fitting parameters.  $f_{on}$  is an order of magnitude larger than  $f_{off}$ , and they both have effect on the magnitude of the change of  $\frac{dw}{dt}$ .  $i_{on}$  and  $i_{off}$  confine the current threshold effectively.  $a_{off}$  forces the upper bound and  $a_{on}$  forces the lower bound for  $\frac{dw}{dt}$ .

### 4)TEAM model

The TEAM model ThrEshold Adaptive Memristive Model [32] is a flexible and convenient model used for characterizing different memristive devices. In this model, a current threshold and tunable nonlinear dependence between current and derivative of the state variable has been suggested. The current-voltage relationship can be both polynomials as well as exponential. The derivative of the state variable for this model is expressed in (9).

$$\frac{dx(t)}{dt} = \begin{cases} k_{off} \cdot \left(\frac{i(t)}{i_{off}} - 1\right) \cdot f_{off}(x), 0 < i_{off} < i \\ 0, & i_{on} < i < i_{off} \\ k_{on} \cdot \left(\frac{i(t)}{i_{on}} - 1\right) \cdot f_{off}(x), i < i_{on} < 0, \end{cases}$$

(9)

## 2.5 Summary of Chapter 2

In this chapter, memristor devices and memristor crossbar arrays were introduced. Some of the applications of crossbar arrays were also described. An application independent testing methodology is of great importance for testing memristor circuits used in these different crossbar applications. Finally, some of the memristor mathematical models were described in brief. These complex mathematical models are a function of voltage, time, and frequency but all of them rely on the concept of  $R_{on}$  and  $R_{off}$ . For my research, a simple resistive model is sufficient for testing purposes to represent whether a memristor is in a low resistance state or in a high resistance state.

## Chapter 3

#### Sneak Path Characterization in Memristors

Note: Some of the contents of this chapter have been published below:

Rasika Joshi, John M Acken, "Sneak Path Characterization in Memristor Circuits", in *Journal of Electronics*, 2020. DOI: 10.1080/00207217.2020.1843716

Sneak path currents impact the performance of resistive crossbar array-based systems. It could have undesired effects on the reading and writing operations of the array based on the size of the array, memristor programming, input voltage and I/O switch vectors. Therefore, it is essential to characterize sneak paths and sneak path currents for understanding the constraints to the memristor crossbar operations. It will help to understand the design limitations when setting the size of a memristor array. A calculation model has been proposed for finding the length of different sneak paths for a given array size. These sneak paths have been analyzed based on the size of the array and the LRS/HRS memristor programming.

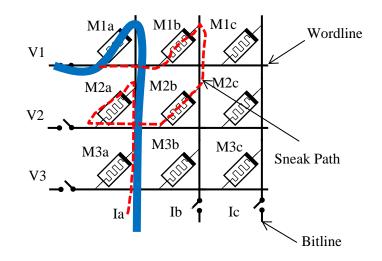

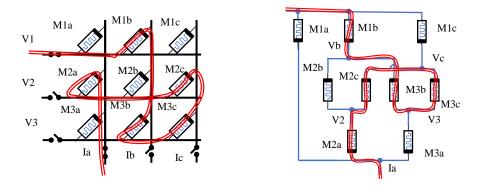

# 3.1 Introduction to Sneak Paths

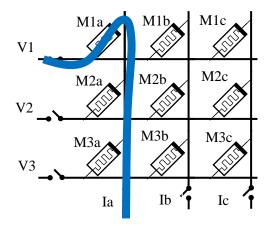

Sneak paths are paths for current parallel to the primary current path occurring in memristor crossbar circuits. The bidirectional nature of memristors allows sneak paths in crossbar arrays. Sneak paths may corrupt the output current causing incorrect read and write operations in memory arrays. Fig. 12 shows a sneak path current example in a 3x3 crossbar circuit. The current flow highlighted in the bold blue line in Fig. 12 is the desired path of current flow through the selected cell at the intersection between the column and the row

of interest called as the primary current. Unfortunately, this ideal case is not the only path, and the current flows through an example sneak path highlighted in the dotted line in red, as shown in Fig 12. The sneak paths depend on the content of the memory and paths with lesser resistance and more memory content will sneak more current [33].

Fig. 12 Ideal case of current flow through a memristor cell and sneak path flow of current in a crossbar array.

## 3.2 Definition of IO switch-vector

The IO test vector set for a memristor crossbar array consists of the IO switch-vector settings for the rows (input) and columns (output). In a crossbar array of size mxn, the wordlines are the horizontal connections and the bitlines are the vertical connections. m is defined as the number of rows or wordlines,  $m_{open}$  is defined as the number of wordlines open, and  $m_{closed}$  as the number of wordlines closed. A wordline closed means that the input voltage source is connected to that wordline and a wordline open is not connected to a voltage source. When a wordline is closed, it is called a selected wordline.  $X_i$  is the switch state for the  $i^{th}$  row, where "1" is closed and "0" is open. n is defined as the number of

columns or bitlines,  $n_{open}$  as the number of bitlines open, and  $n_{closed}$  as the number of bitlines closed. A bitline closed means that the grounded current sensor on that column output is connected to that bitline and a bitline open is not connected to a grounded output current sensor. A bitline closed is called a selected bitline.  $Y_j$  is the switch state for the  $j^{th}$  column, where "1" is closed and "0" is open. In summary, the input state of  $X_1X_2...X_n$  is combined with the output state of  $Y_1Y_2...Y_j...Y_n$  to define the I/O switch-vector of  $X_1X_2...X_mY_1Y_2...Y_n$ .

3.3 Sneak Path Formula for number of sneak paths in crossbar arrays

The total number of sneak paths in a crossbar circuit is a function of the input conditions, array size and memristor programmed values. When all the memristors in the crossbar array are of equal resistance, all the sneak paths are three memristor long. The number of three memristor long sneak paths is expressed as  $n_{3mem}$  in (10):

$$n_{3mem} = m_{open} * m_{closed} * n_{open} * n_{closed}$$

(10)

When all the memristors in the crossbar array have equal resistance, the total number of three memristor long sneak paths in mxn circuit is the product of the bitline and wordline switches that are being switched on or off as shown in (10).  $X_i, X_{i+1}, X_{i+2}...X_m$  are defined as the switches representing the wordlines to be switched on or off and  $Y_j, Y_{j+1}, Y_{j+2}...Y_n$  are defined as the switches representing the bitlines of the crossbar array. For example, 3x3 circuit as shown in Fig. 12, the I/O switch vector is 100100. For a 2x2 circuit, considering the I/O switch-vector is  $X_1X_2Y_1Y_2 = 1010, m_{open} = 1, m_{closed} = 1, n_{open} = 1$  and  $n_{closed} = 1$ . The

total number of three memristor long sneak paths in this 2x2 array example is 1. For bigger memristor arrays, for example in an 8x8 circuit, the I/O switch-vector is  $X_IX_2X_3X_4X_5X_6X_7X_8$  $Y_1Y_2Y_3Y_4Y_5Y_6Y_7Y_8 = 1000000010000000$ ,  $m_{open} = 7$ ,  $m_{closed} = 1$ ,  $n_{open} = 7$  and  $n_{closed} = 1$ . The total number of possible three memristor long sneak paths for this 8x8 array example is 49. Some input/output combinations do not have sneak paths. When all the row switches or column switches are on, there would be no sneak paths. For there to be sneak paths, there should be  $m > m_{open} \ge 1$  and  $n > n_{open} \ge 1$  on the input and output respectively.

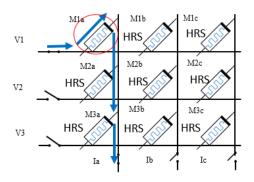

# 3.4 Analysis on Length of Sneak paths in crossbar arrays

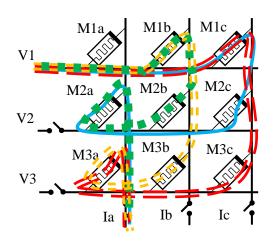

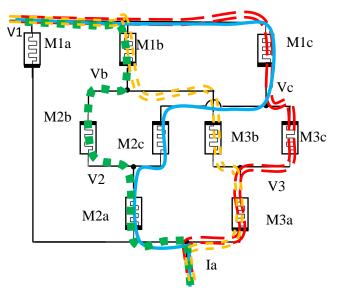

The length of a sneak path is a function of input conditions, array size and memristor programmed values. HRS refers to the high resistance state and LRS refers to the Low resistance state of the memristor. A 3x3 crossbar array example with memristors labelled from *M1a*, *M1b*, *M1c* through *M3c* with all memristors having equal resistance values is considered. *V1*, *V2*, *V3* are the input voltages to the crossbar array and *Ia*, *Ib*, *Ic* are the output currents. In Fig. 13, the I/O switch-vector is  $X_1X_2X_3 = 100$  and  $Y_1Y_2Y_3 = 100$  for input voltages and output currents respectively. The primary current is the current through the selected cell or cells in the crossbar array. The selected cells are memristors at the intersection of the selected bitlines and the selected wordlines. *I*<sub>primaryj</sub> is the output current for selected cells on column j. Sneak path current is the current through the non-selected cells in the crossbar array (*I*<sub>sneakj</sub>).

$$I_{outputj} = I_{primaryj} + I_{sneakj}$$

(11)

The output current is the sum of the primary current and the sneak path current as shown in (11). One metric for characterizing sneak path current is the relative magnitude of the primary current to the sneak path current and its effect on the output current.

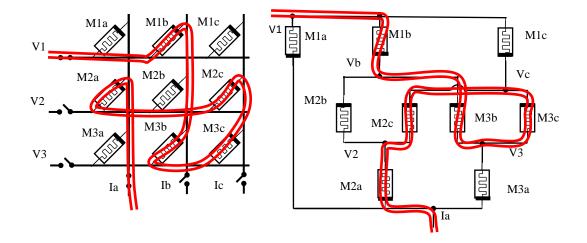

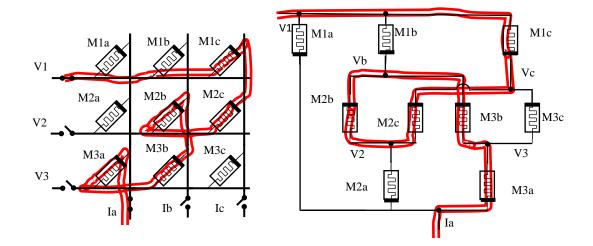

Fig. 13 3x3 Crossbar array with I/O switch-vector = 100100.

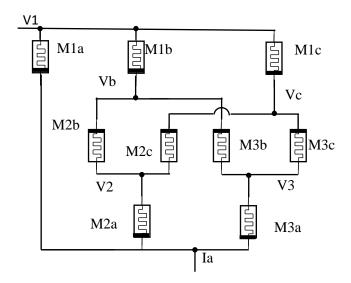

The circuit representation for this crossbar example is shown in Fig. 14. Notice that this circuit is not a mesh. The primary path is through selected cell *M1a*. The half-selected cells in this circuit are the ones sharing the line with *M1a*, namely *M1b*, *M1c*, *M2a* and *M3a*. The sneak paths through the electrical network are three memristor long as shown in Fig. 14, namely *M1b-M2b-M2a*, *M1b-M3b-M3a*, *M1c-M2c-M2a*, and *M1c-M3c-M3a*. The total number of possible I/O switch-vectors for an *mxn* crossbar circuit is expressed by (12), and the total number of I/O switch vectors that create sneak paths is shown in (13).

$$Total num I/0$$

switch-vectors =  $(2^m - 1) * (2^n - 1)$ . (12)

Total num sneak path

$$I/O$$

switch-vector =  $(2^m - 2) * (2^n - 2)$ . (13)

Fig. 14 Circuit diagram for 3x3 memristor array with I/O switch-vector = 100100.

The I/O switch-vectors where all wordlines and/or all bitlines set to floating condition are not being considered. For example, in a 4x4 crossbar circuit, the total number of possible functional I/O switch-vector cases are 225. Out of the 256 possible I/O switch vector combinations 31 are not functional because either all the inputs or all the outputs are disconnected. When all the inputs are 0 or all the outputs are 0, the crossbar array is disconnected and not functioning. There are 16 input switch vectors with all the outputs 0 plus 16 output switch vectors where all the inputs are 0, minus 1 for the repeated case of all zeroes on both input and output for a total of 31 non-functional I/O switch vectors. For the 4 x 4 crossbar circuit example, the total number of possible sneak path I/O switch vector cases is 196. As noted previously, if all the memristors have the same resistance values, then all the sneak paths are of length three. For example, consider the crossbar array shown in Fig. 15.

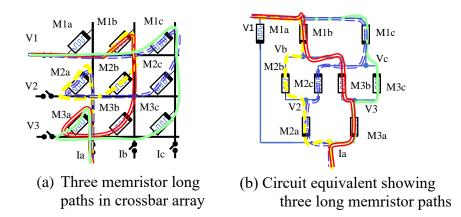

(a) Three memristor long paths in crossbar array

(b) Circuit equivalent showing three memristor long paths

|      | M1b-M2b-M2a |

|------|-------------|

| ===: | M1b-M3b-M3a |

|      | M1c-M2c-M2a |

| ===  | M1c-M3c-M3a |

Fig. 15 Sneak paths of length 3 in a 3x3 crossbar array with I/O switch vector = 100100

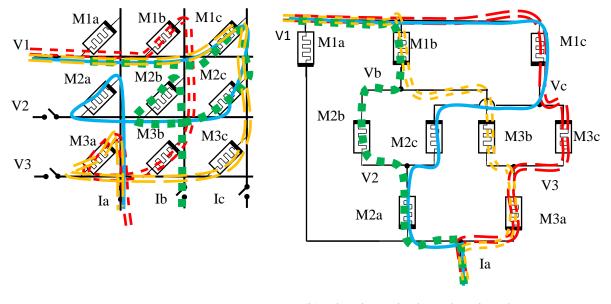

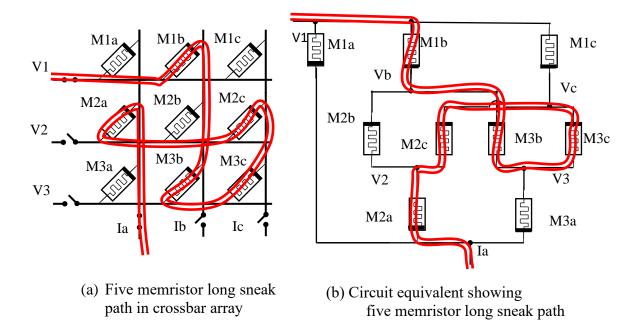

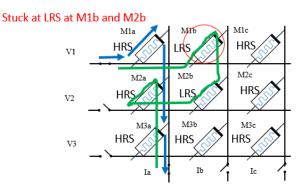

The three memristor long sneak paths are: *M1b-M2b-M2a*, *M1b-M3b-M3a*, *M1c-M2c-M2a*, and *M1c-M3c-M3a* as mentioned above. However, when the memristors are at different resistance values, some patterns can create longer sneak paths. The four possible five memristor long memristor sneak paths are: *M1c-M2c-M2b-M3b-M3a*, *M1c-M3c-M3b-M2a*, *M1b-M2b-M2c-M3c-M3a*, and *M1b-M3b-M3c-M2c-M2a*. One way to get the five-long path *M1c-M2c-M2b-M3b-M3a* is to have *M1b* and *M2a* in the HRS and the rest

in the LRS. Another programming to get the same long sneak path is *M1b*, *M2a*, and *M3b* in the HRS with the rest in LRS. To get the second example of the five memristor long sneak path, *M1c-M3c-M3b-M2b-M2a*, the memristors *M1b* and *M2c* are programmed to the HRS and the rest are LRS. To get the fourth example of path *M1b-M3b-M3c-M2c-M2a*, the memristors *M1c*, *M2b*, and *M3a* are in the HRS. This case is shown in Fig. 16 highlighted in red. There are many other patterns to get these and the other five memristor long sneak paths for a specific HRS/LRS programming pattern. Even with the five memristor long sneak paths there are still a total of four sneak paths. Specifically, three of the paths are three memristor long (*M1b-M2b-M2a*, *M1b-M3b-M3a*, *M1c-M2c-M2a*) and one of the paths is five memristor long (as shown in Fig. 16).

Fig. 16 Sneak path M1b-M3b-M3c-M2c-M2a of length 5 in a 3x3 crossbar array with M1c=M2b=M3a=HRS and remaining memristors in LRS for I/O switch vector =100100.

As shown in Table 1 and (14), for this 3x3 array the total number of longest possible sneak paths is 4. The length of sneak paths is a function of the array size, the I/O switch-vector, and the programming of the individual memristors. The formulas for the different lengths of sneak paths for square array sizes (i.e. m=n) have been derived.

| Array<br>size | I/O switch-vector | 3 long paths | 5 long<br>paths | 7 long<br>paths        | 9 long paths          |

|---------------|-------------------|--------------|-----------------|------------------------|-----------------------|

| 3x3           | 001 001           | 4            | 4               | -                      | -                     |

| 4x4           | 0001 0001         | 9            | 36              | 36                     | -                     |

| 5x5           | 00001 00001       | 16           | 144             | 576                    | 576                   |

| 6x6           | 000001 000001     | 25           | 400             | 3600                   | 14400                 |

| 7x7           | 0000001 0000001   | 36           | 900             | 14400                  | 129600                |

| 8x8           | 00000001 00000001 | 49           | 1764            | 44100                  | 705600                |

| 9x9           | 00000001 00000001 | 64           | 3136            | 112896                 | 2822400               |

| 100 x100      | 0001<br>0001      | 9801         | 94128804        | 8.86 x10 <sup>11</sup> | 8.16x10 <sup>15</sup> |

Table 1 Count of Possible Different Length Sneak Paths in Crossbar Circuits

From Table 1, the long length sneak paths for any array size are calculated using the formulas below. For three memristor long, five memristor long, seven memristor long and nine memristor long sneak paths, the possible number of sneak paths can be calculated as below:

$$n_{3mem} = (n-1)^2 \tag{14}$$

$$n_{5mem} = (n-1)^2 * (n-2)^2 \tag{15}$$

$$n_{7mem} = (n-1)^2 * (n-2)^2 * (n-3)^2$$

(16)

$$n_{9mem} = (n-1)^2 * (n-2)^2 * (n-3)^2 * (n-4)^2$$

(17)

When all the memristors are programmed to the same resistance value of LRS or HRS, all the sneak paths are three memristor long. Therefore, every three memristor path parallel to the target memristor is a sneak path. For a *nxn* array, that is  $(n-1)^2$  paths. This is derived because there are (n-1) parallel memristors on the selected bitline and (n-1) parallel memristors on the selected wordline to the target memristor. There is a different unselected memristor connecting each selected bitline memristor to each selected wordline memristor. There are (n-1) unselected bitlines and (n-1) unselected wordlines hence  $(n-1)^2$  different memristors each resulting in a unique sneak path. To achieve a five memristor long sneak path, two or three of the memristors need to be programmed as HRS and the remaining are programmed to LRS. The other two equations follow similar path with more memristors in HRS.

Considering a memristor crossbar circuit consisting of all low resistance programming or all high resistance programming, the following observations for the number and length of sneak paths have been made

- (1) If  $n_{closed} = n \text{ OR } m_{closed} = m$  for inputs and outputs switches then there will be no sneak paths.

- (2) If there is at least one *n*<sub>open</sub> in the input AND at least one *m*<sub>open</sub> in the output, the length of the sneak path is always of three memristors. This only applies when all the memristors are of equal value.

- (3) When the memristors are not of equal value, the length of the longest possible sneak path ( $L_{max}$ ) is expressed by (18):

$L_{max} = 2 * n - 1 \quad \text{for } n \le m \tag{18}$

- (4) The minimum number of  $n_{open}$  or  $m_{open}$  on inputs or outputs sets the path length. If  $n_{open} = 2$  in the input AND  $m_{open} = 2$  in the output, the longest possible sneak path will be of five memristor length. Similarly if  $n_{open} = m_{open} = 3$  then a maximum possible length of seven memristors and so on. This applies when certain patterns of memristors are being programmed to high/low resistance value as discussed in Fig. 16.

- (5) The lowest number of rows or columns sets the maximum length of the sneak paths. For example in 2x3, 2x2, and 3x2 arrays, the longest length sneak path is three memristors.

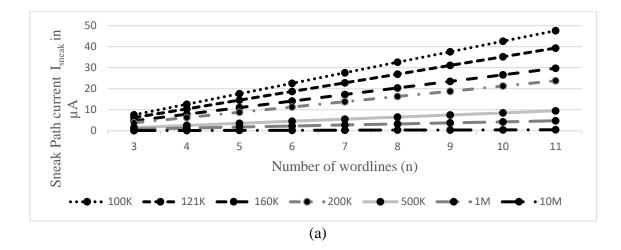

- 3.5 Analysis of Sneak Path Currents in Crossbar Arrays

The sneak path current significantly impacts the design space for a memristor array. The research addresses two questions about sneak path impact: 1) The effect of different parameters and conditions on the behaviour of sneak paths that in turn affect the memristor crossbar array performance; 2) the impact of sneak path current with respect to size of memristor array, memristor resistances, I/O switch-vector, high/low programming of the memristors. These effects set the boundaries and limits for the design space. A similar sneak path current analysis has been described in [34]. Tang Zhensen *et al.* [34] analyses the worst-case scenario for read operations that include the worst-case selected location and worst-case data pattern based on the effect of sneak paths and interconnection resistances. However, my research's characterization is for various cases (not just the worst case) and resistance values. In [8], the parameters for limiting the array size were first chosen such as the line resistance and non-linear device characteristics and then the sneak

path current was analysed. In contrast, the proposed sneak path current analysis helps to determine the boundary conditions for crossbar arrays. Also, the formula for sneak path calculation derived in [8] is based on equal values of memristors. In contrast, my proposed characterization includes various programming of memristor values and varying I/O switch-vectors. Cassuto paper [35][36] gives mathematical proofs for a sneak-path free readout and coding schemes to eliminate sneak paths. Their schemes are concentrating on eliminating sneak paths for read error-free column readouts in their application. Whereas, my research analyses the impact of different memristor parameters and operating conditions (such as I/O switch-vector and programming patterns for memristors in high resistance state (HRS) and low resistance state (LRS) on the behaviour of the sneak path currents, and in turn, the memristor output current for any given crossbar array application. For example, the size of the memristor array can be determined for a memristance range before the sneak path current interferes with the crossbar operation. For my research, memristor arrays with bidirectional memristors are being considered, and not rectifying memristors. The conditions/parameters looked at are the high/low programming of memristors, I/O switch-vectors (row and column selectors) – non-selected, selected and half-selected cells in the memristor crossbar circuit, square-non/square arrays, and ranges of memristor resistance.

Based on the results, curve fitting models for calculating the sneak path currents as a function of array size, memristor resistances, memristor programming, I/O switchvectors and input voltage are determined. The characteristics of the complete relationship between memristor parameters (such as array size, high-low memristance ratios) and the sneak path current will provide a basis for design implementation trade-offs.

### 3.5.1 Sneak Path Current Calculation tool

The sneak paths were found using a python based sneak path calculator. The sneak path calculator gives the sneak paths for varying array sizes based on the sneak path algorithm discussed in theory. The calculator also generates a text file output directly fed into the LTspice simulator tool to simulate the output currents based on the resistance and input voltage values. Sneak path current analysis is based on these simulated currents. Here are the following steps to generate the LTSpice circuit using the python calculator:

- The number of wordlines and number of bitlines is taken from the user to create the I/O switch vector combination.

- (2) The input voltage and the LRS/HRS value of the memristors are also taken as user inputs.

- (3) The number of sneak paths is determined using the equation (14) through (17).

- (4) The target memristor is identified from the I/O switch vector combination. All the memristors excluding the target memristor are used to create the sneak path circuit.

- (5) Sneak paths are generated based on the model discussed for equation (14).

- (6) The circuit node connections are assigned based on the sneak path information.

- (7) The python generator outputs a file that is fed to the LTspice tool.

- (8) The sneak path current is simulated in LTspice based on the user input voltage and resistance values.

3.6 Sneak Path Current Analysis w.r.t size of array and resistance programming

Crossbar array applications require quantitative analysis of array characteristics especially sneak path currents to provide boundary conditions for designing crossbar arrays. In the following sections, sneak path currents have been analysed with respect to different parameters such as the size of the array, resistance programming, input voltage and input/output conditions. My research presents equations based on simulation results for determining the sneak path current as a function of the memristor array parameters. The derived equations will help with the sneak path current prediction of any array size for understanding the constraints to the memristor crossbar operation.

# 3.6.1 Resistance Programming

Various technologies and models use different values of memristor resistance. Table 2 shows different published ranges of resistances for the low and high resistance states. For our initial data analysis, the low resistance value of  $10K\Omega$  and high resistance values of  $1M\Omega$ ,  $50K\Omega$  and  $500K\Omega$  have been used. The design decisions based upon sneak path current are a function of the range of resistances, the ratio of the high-low resistances, and the ratio of memristor resistance to the line resistance. The sneak path current characterization includes the effects of different memristor resistance values.

| Paper                                                                                                    | HRS High<br>Resistance | LRS Low<br>Resistance |

|----------------------------------------------------------------------------------------------------------|------------------------|-----------------------|

| Fault Modeling and Parallel Testing for<br>1T1M Memory Array [37]                                        | 1ΜΩ                    | 10K <b>Ω</b>          |

| A bridge technique for memristor state<br>programming [38]                                               | 100KΩ                  | 100Ω                  |

| A Test Method for Finding Boundary<br>Currents of 1T1R Memristor Memories<br>[39]                        | 500ΚΩ                  | 10K-<br>160KΩ         |

| Modeling Detection, and Diagnosis of<br>Faults in Multilevel Memristor Memories<br>[40]                  | 200ΚΩ                  | 100Ω                  |

| Sneak-Path Testing of Crossbar-Based<br>Nonvolatile Random-Access Memories<br>[41]                       | 121 <b>KΩ</b>          | 121Ω                  |

| Sneak Path Based Test for 3D-Stacked<br>One Transistor N-RRAM array [42]                                 | 500ΚΩ                  | 10 <b>ΚΩ</b>          |

| Design and Optimization of a Strong<br>PUF Exploiting Sneak Paths in Resistive<br>Cross-point Array [43] | 10MΩ                   | 100ΚΩ                 |

| Sneak-Path Based Test and Diagnosis for<br>1R RRAM Crossbar Using Voltage Bias<br>Technique [9]          | 200ΚΩ                  | 100Ω                  |

Table 2 Low and High Resistance Values for Memristors

Sneak path current is specifically affected by  $R_{HRS}/R_{LRS}$  ratio. As quoted in [10][44][45], the typical ratio of  $R_{HRS}$  to  $R_{LRS}$  is  $10^2 - 10^3$ . Analysing Table 2 confirms their ratio. My research contribution uses  $R_{HRS}/R_{LRS}$  ratios from 2 to 100. The paper [46] evaluated  $R_{HRS}/R_{LRS}$  ratios from array sizes from 10 to 50. They found out by spice simulation that the sneak path current needs to be limited as a function of  $R_{HRS}/R_{LRS}$  ratio.

Another reference [32] recommends a high ratio between  $R_{HRS}/R_{LRS}$  to store distinct Boolean data in a memristive device.

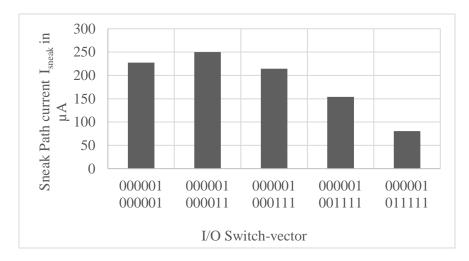

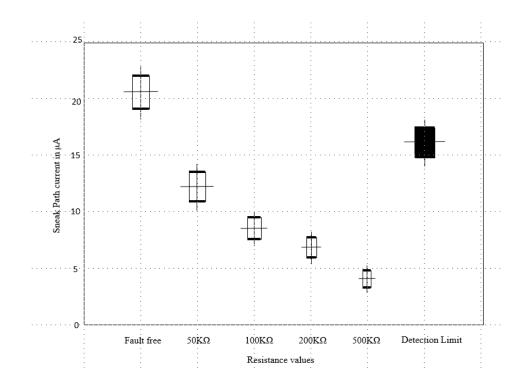

The simulated sneak path currents for the different IO switch-vector combinations discussed in the sections below are of two types. The first type is called the *total sneak path current*, defined as the sneak path current measured for all the sneak paths in a crossbar array with single bitline output. The second type of sneak path current is called as *sneak path current per array bitline output* where the sneak path current is measured from a single output in an IO switch-vector having multiple bitline outputs.

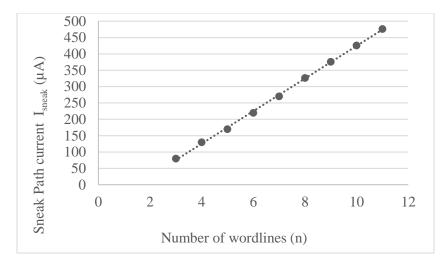

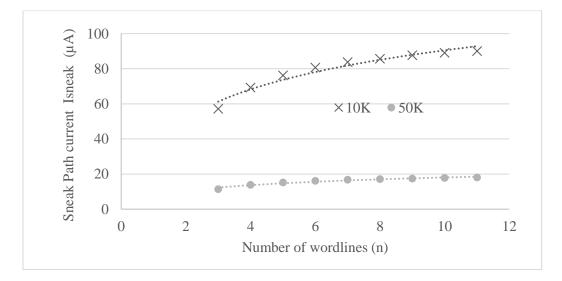

3.6.2 Sneak Path Current for IO switch-vector  $m_{closed} = n_{closed} = 1$

Considering the I/O switch-vectors set to one switched on input and one switched on output (i.e.  $m_{closed} = 1$  and  $n_{closed} = 1$ ), the following trend in the sneak path current values is observed in Fig. 11. The sneak path current measured for this IO switch-vector is the total sneak path current. The sneak path currents ( $I_{sneak}$ ) is plotted on the Y axis and the size of side of the crossbar array (n) on the X axis. From the graph, the equation that is observed is  $I_{sneak} = 49.8 * n-73.9 \,\mu\text{A} [I_{sneak} = A * n + B]$  where  $A = \sim 50 \,\mu\text{A}$  and the offset  $B = \sim -74 \,\mu\text{A}$ . Here A is the function of the resistance in the crossbar circuit and the input voltage applied to the wordlines and is equal to (0.5/R) \*V. The sneak path current relationship for Fig. 17 is shown in (19). The offset is derived from curve fitting.

$$I_{sneak} = \frac{0.5}{R} * V * n + offset$$

(19)

Fig. 17 Sneak Path current analysis for one input ON and one output ON  $[m_{closed} = n_{closed} = 1]$  for LRS programming of 10K $\Omega$  where m=n.

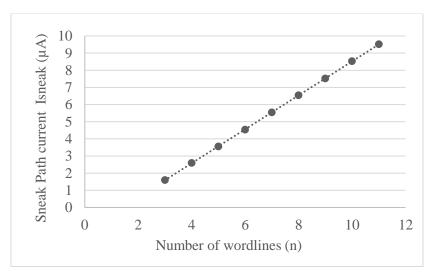

Fig. 18 Sneak Path current analysis for one input ON and one output ON for  $[m_{closed} = n_{closed} = 1]$  HRS programming of 500K $\Omega$  where m=n.

This equation is followed for other memristance values of R. Fig. 18 shows the sneak path current values with HRS programming of 500K $\Omega$ . Here, the equation of the graph seen is  $I_{sneak} = 0.99 * n - 1.37 \ \mu$ A where the slope A = 0.5/500K $\Omega = 1$  $\mu$ A and offset  $B = -1.37 \ \mu$ A. A linear curve has been observed for these two graphs with 10K $\Omega$  and 500K $\Omega$

resistance values with a slope of 0.5/R. Predictions can be made on sneak path current for larger array sizes and a variety of high/low resistance values using equation (19).

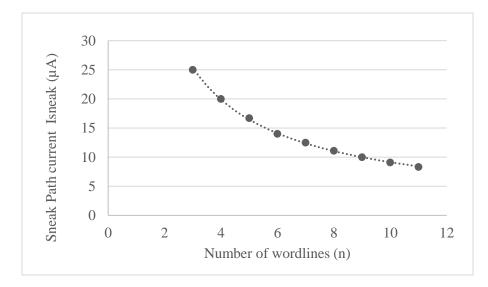

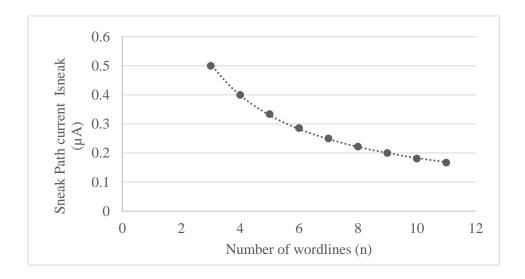

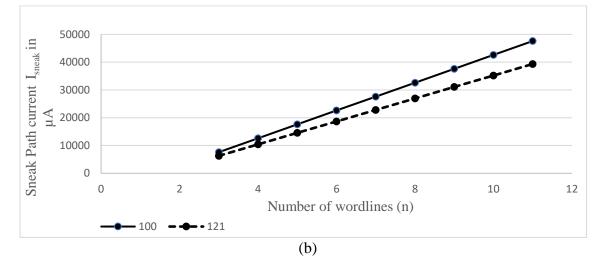

3.6.3 Sneak Path Current for IO switch-vector  $m_{closed} = m-1$ ,  $n_{closed} = n-1$

Considering another case of I/O switch-vector such as 011 011 for a 3x3 memristor array where  $m_{closed} = m-1=2$  and  $n_{closed} = n-1=2$ , the sneak path current results for each array output can be observed for low resistance of 10K $\Omega$  and high resistance of 500K $\Omega$  in Fig. 19 and Fig. 20 respectively. For this IO switch-vector combination, the sneak path current measured is the *sneak path current per array bitline output*. The equation of the sneak path current for this IO switch-vector can be expressed as shown in (20).

$$I_{sneak} = C * n^{-0.85}$$

(20)

The scaling factor  $C = 64.5 \mu A$  for LRS programming of  $10K\Omega$  and  $C = 1.29 \mu A$  for HRS programming of  $500K\Omega$ . The impact of the offset value decreases with the increase in the size of the array. A power curve is observed for these two graphs with an exponential constant of -0.85 for these low and high resistance programming values.

Fig. 19 Sneak Path current analysis for m–1 inputs ON and n–1 outputs ON [ $m_{closed} = m-1$ ] for LRS programming of 10K $\Omega$  where m=n.

Fig. 20 Sneak Path current analysis for m–1 inputs ON and n–1 outputs ON [ $m_{closed} = m-1$ ] for HRS programming of 500K $\Omega$  where m=n.

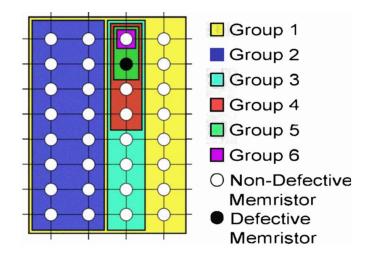

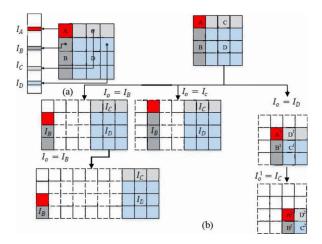

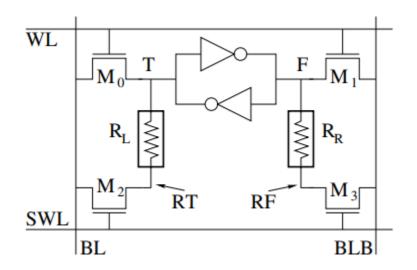

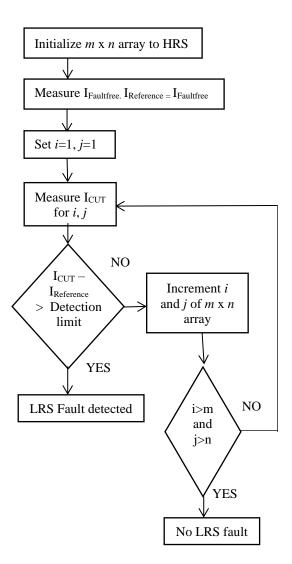

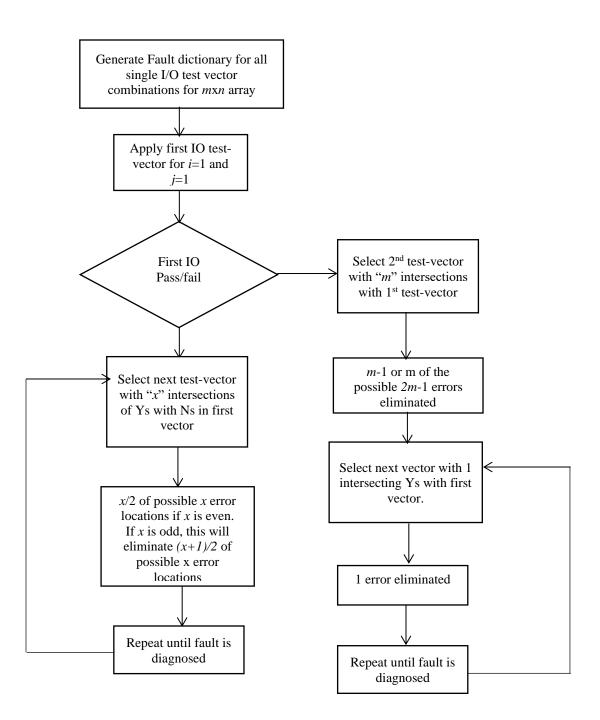

As shown in Fig. 19 and Fig. 20, the sneak path current may seem decreasing with the increase in the size of the array. However, one note is that this sneak path current is analysed per array output. For a 3x3 array, the sneak path current for 011 011 I/O switch-vector combination is  $25\mu$ A per each array output with input voltage = 1V and all LRS =